前回は RSフリップフロップのおさらいをしました。

今回も RS フリップフロップですが、入力をクロックで同期できるタイプのものを試してみます。

ゲート型 RS フリップフロップ

実験回路

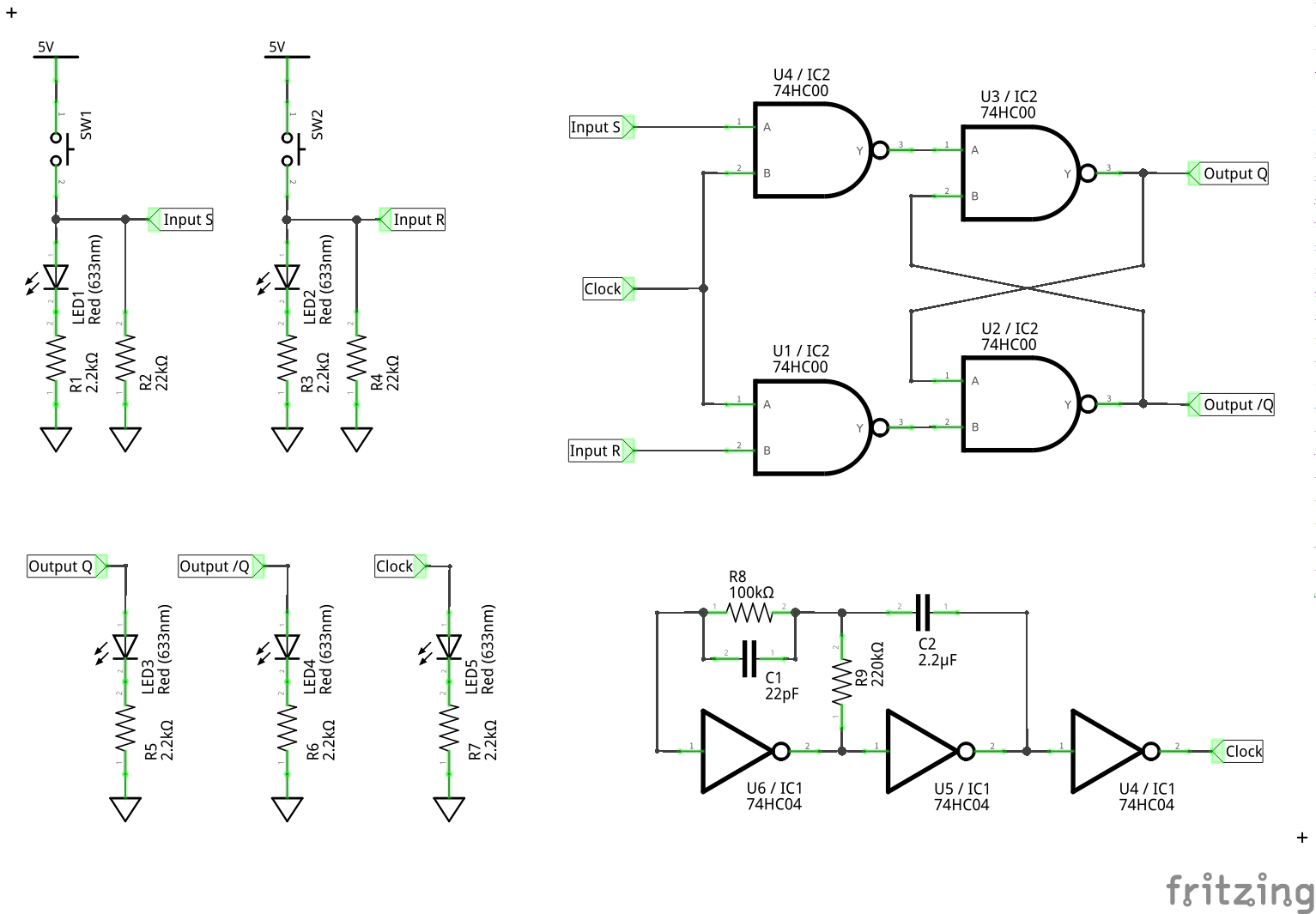

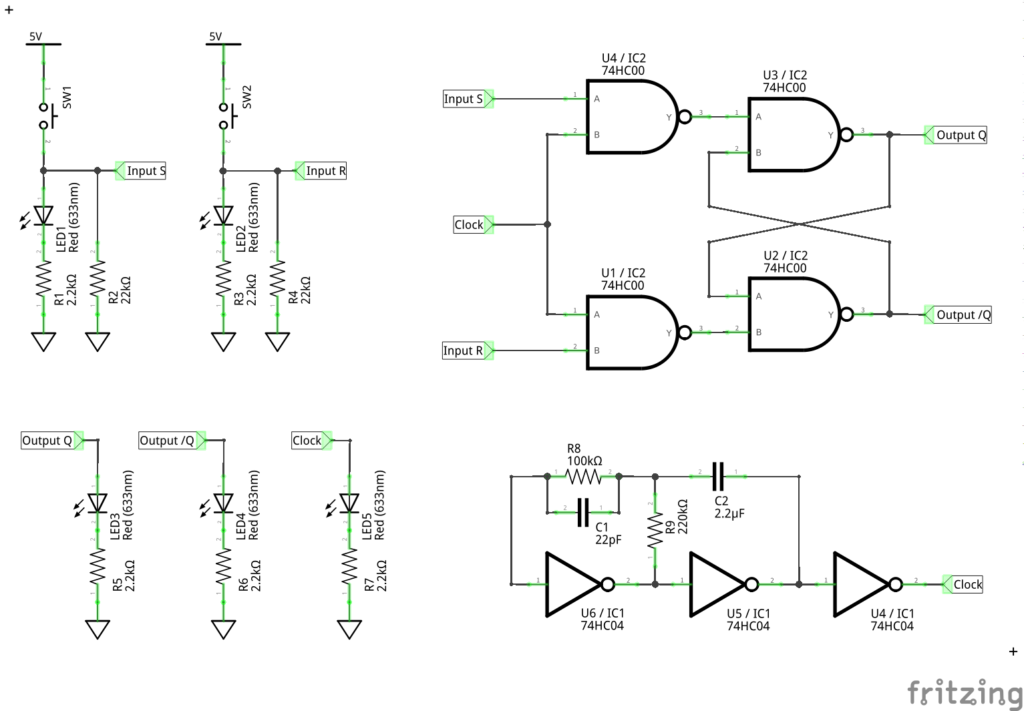

前回 NAND で作った RS フリップフロップを、ちょっと改造して、クロックを入力できるようにしました (図 1)。

| Clock | S | R | Q | Q |

| 0 | X | X | Qn | Qn |

| 1 | 0 | 0 | Qn | Qn |

| 1 | 0 | 1 | 0 | 1 |

| 1 | 1 | 0 | 1 | 0 |

| 1 | 1 | 1 | 禁 | 止 |

NOT になっていた R と S の入力ゲート部分を NAND にし、それぞれにクロックを入力します。これにより、クロックが “1” のときだけ、R、S の入力が有効になります。クロックが “0” の間は、R、S が変化しても出力は変化しません。

クロックに同期する、っていうのとはちょっと雰囲気が違いますね。

クロックによって入力ゲートが開閉するので、「ゲート型」といわれます。また、クロックが “0” になって入力ゲートが閉じると、その直前の出力状態が保持されます。”0 ” か “1” かの 2 つの状態が保持されるので、「バイステーブル・ラッチ」ともいわれるようです。

右下部分がクロックの発振回路です。インバータ 74HC04を 3 個使っていますが、U6、U5 が矩形波発振回路 (過去記事)、U4 はバッファです。周期 1000ms、デューティ比 50% になっています。

回路の動作

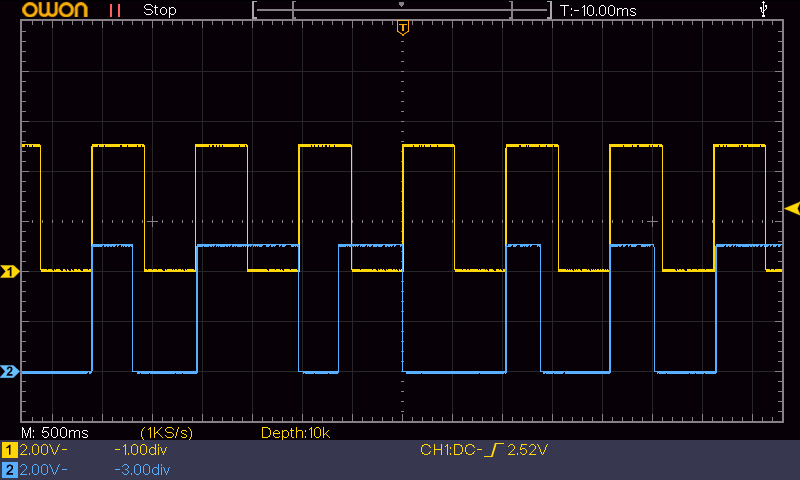

ゲート型 RS フリップフロップの動作波形をみてみましょう (図 3)。

「禁止」なときの動作

禁止されている、両方の押しボタンを同時に押したときは、どうなるでしょうか?

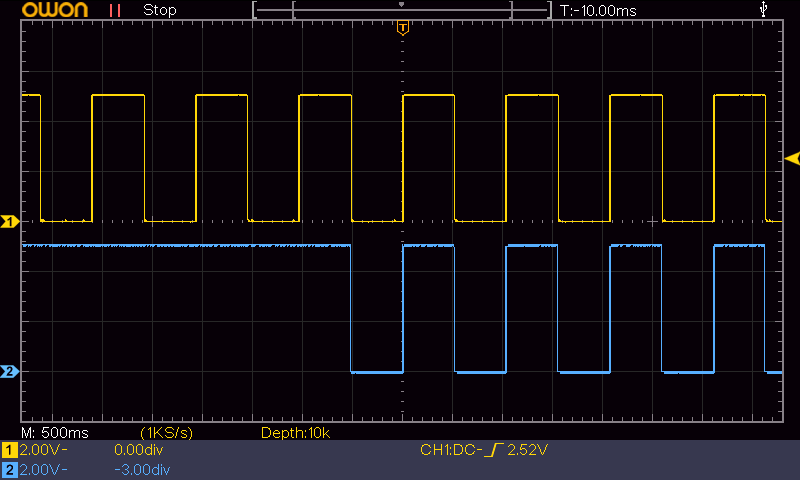

図 4 の、前半は SW1 のみ押している S=1 の状態です。出力 Q は “1” で保持されています。

ここで SW2 も押して S=R=1 にします。

クロックが “1” のとき、U4、U1 の出力がともに “0” の禁止の状態で、出力は Q=Q=1 です。

クロックが “0” になったときにどうなるかは、前回 RS フリップフロップの実験でもやりましたね。どちらかに転びます。どっちに転ぶかは回路の個性です。今回の実験では Q=0、Q=1 になりました。

オシロスコープのプローブをあてたりして回路の状態が変化すると、たまに出力が発振しました。ん?出力かな? クロックも異常発振してたけど、電源からまわったのかな。

とにかく、この回路では、「禁止」状態から遷移すると「不定」ではなくて、「不安定」な感じです。

後記

ゲート型 RS フリップフロップって、なにか利用方法あります? 思い浮かばない (;´Д`)

が、次に実験してみようと考えているプライマリ・レプリカ型 RS フリップフロップでは、入力ゲートが活躍します。ゲート型を理解した上で、つぎ、いってみましょう (^_^;)

論理回路 / 基本的な論理回路

論理回路 / RSフリップフロップ

論理回路 / ゲート型 RS フリップフロップ

論理回路 / プライマリ・レプリカ型 RS フリップフロップ

論理回路 / Dフリップフロップ

論理回路 / JK フリップフロップ

論理回路 / 分周回路・カウンタ回路

論理回路 / 4進同期カウンタ (2bit)

論理回路 / 8進同期カウンタ (3bit)

論理回路 / 16進同期カウンタ (4bit)

論理回路 / 10進同期カウンタと 7セグメントLED

論理回路 / 半加算器と全加算器

論理回路 / 4ビット加算器の構成とシミュレーション

論理回路 / 4ビット加算器をロジック IC でつくる

加算器でカウンタを作る / 構成とシミュレーション

加算器でカウンタを作る / 16進カウンタ

加算器でカウンタをつくる / 10進カウンタ

論理回路 / シフトレジスタ・ジョンソンカウンタ・リングカウンタ

さらに…