2023.6.9

内容を新しくした記事を投稿しました。こちらも併せてご覧ください。

いつかオシロスコープを買ったら、やりたいと思っていたことがあります。

発振回路を作ってみたい (^_^;)

その夢が叶いましたので、発振回路を作って波形を観察してみましょう。

今回は、デジタル回路のクロックなどに利用する矩形波を、オペアンプを使って作ります。

矩形波発振回路

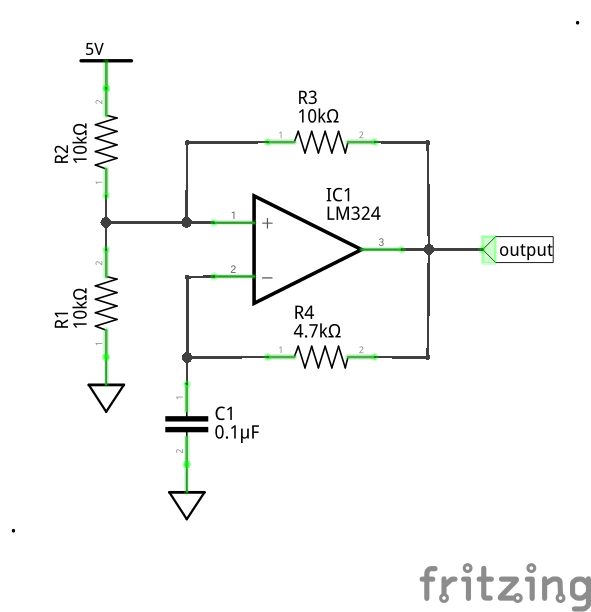

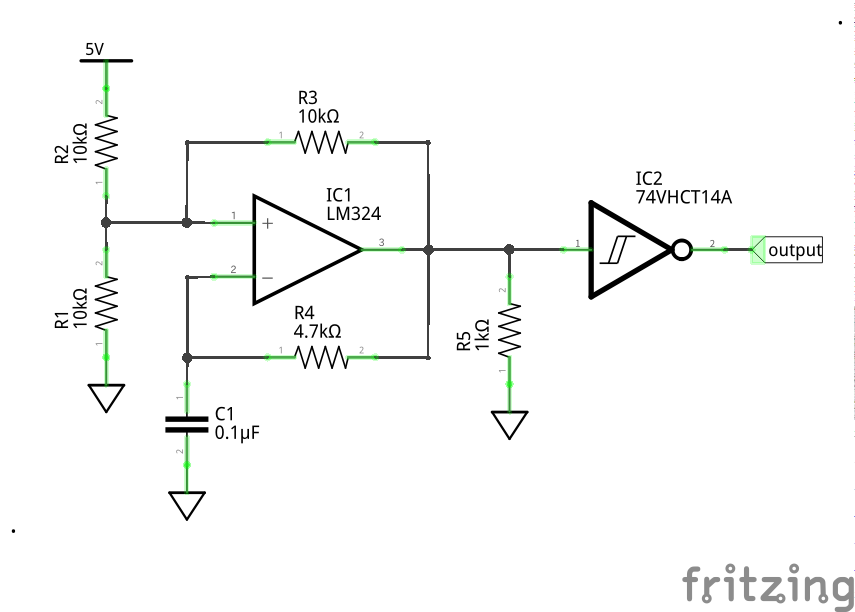

図 (1) は、ググるとよく出てくるオペアンプを使った矩形波発振回路です。汎用オペアンプ LM324 を使って組んでみました。

R1 、R2 、R3 で構成されるのはヒステリシス特性のあるコンパレータ回路。

一般に、R1 、R2 、R3 が同じ値なら、基準となる + 側入力電圧は、出力が HIGH のときに Vcc の 2/3 、LOW のときに 1/3 になる、と解説されています。

したがって、デューティー比は 50% 。

C1 と R4 はいわゆる RC 回路。オペアンプの出力が HIGH の時コンデンサが充電され、LOW になると放電します。

変化するコンデンサの電圧がオペアンプの ー 側入力になり、+ 側の基準電圧と比較されてオペアンプの出力が HIGH になったり LOW になったり、結果、出力が矩形波になる、という仕組みです。

発振する矩形波の周期は、近似値ですが、以下のようになるとのこと。

T = 1.39 CR = 1.39 x 0.1μF x 4.7KΩ = 0.65ms

周波数にすると、1540Hz です。

各部の波形

では、各部の波形を、オシロスコープで観察してみましょう。

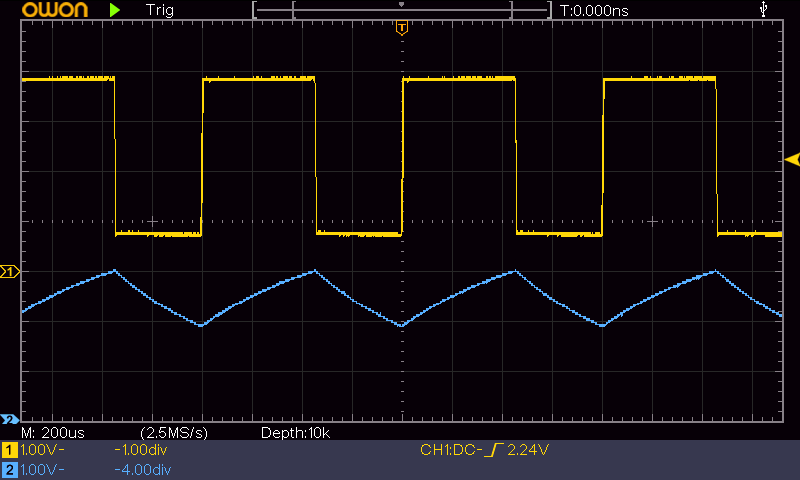

図 (2) の上が、出力波形です。

周期 0.80ms 、デューティー比 54% になりました。

周期は、だいたいが計算式どおりにはなりません。こんなもんです。デューティー比も 50% に拘らないなら、まぁいいんじゃないでしょうか。

下の波形は、コンデンサ C1 の電圧です。3.0V から 1.9V の範囲で変化しています。

ちなみに、これを三角波として利用することもできます。

ついでに、デューティー比の話。

雑談です、テキトーに聞いといて下さい。

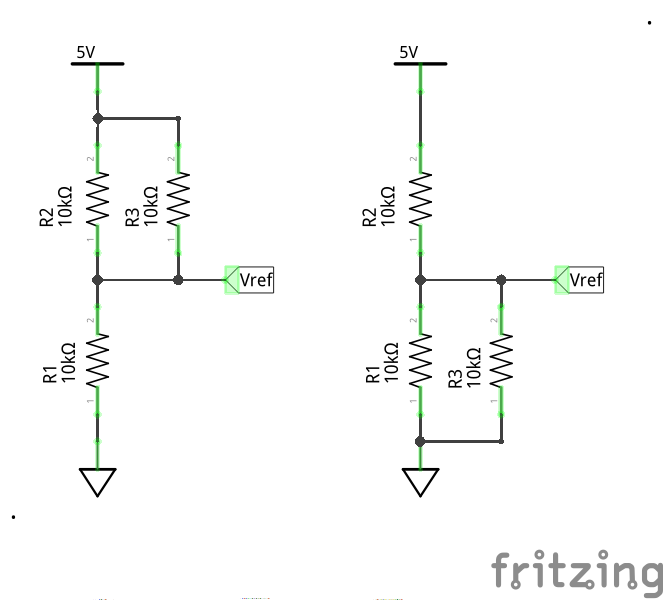

図 (3) は、コンパレータの基準電圧の解説でよく見る抵抗分圧回路です。

分圧回路から出力されるのは、オペアンプの出力が HIGH のときと LOW のとき、それぞれ電源電圧の 2/3 と 1/3 、つまり、3.3V と 1.7V となります。

この場合、デューティー比 50% の矩形波が出力されます。

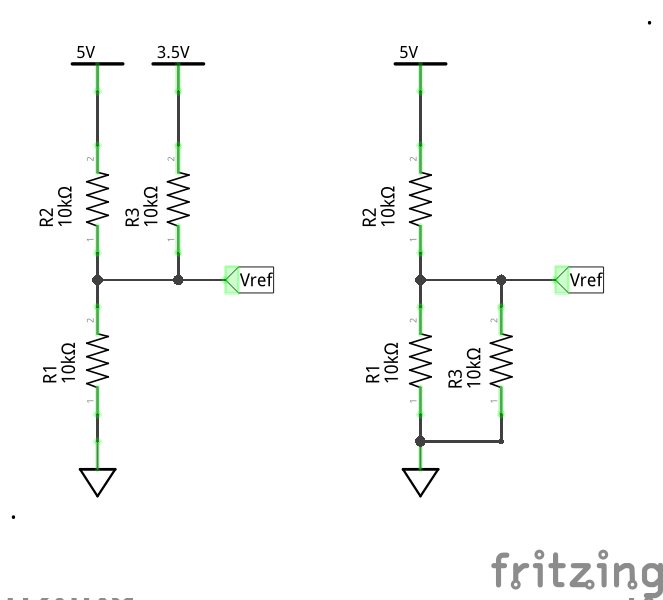

でも実際には、オペアンプの出力電圧はふつう 5V ではありません。たとえば、出力が 3.5V と 0V だとしたら、図 (4) のようになるはずです。

このとき出力される電圧は、2.8V と 1.7V になります。計算方法? 電気回路の基本のキ、キルヒホッフの法則で計算するんですよ。

コンデンサ C1 は、5V ではなく、3.5V を目指して充電されます。基準電圧との差は、1.7V だったものが 0.7V に減りました。そのために、充電にかかる時間が長くなります。

結果、デューティー比が大きくなってしまいます。

波形が汚い?

以前、この発振回路で得られる矩形波をクロックとして、シフトレジスタを使ってみた ことがありますが、うまく動作してくれませんでした。原因は、波形が汚い。対策として、シュミット回路が必要だ、とのこと。

出力波形を拡大してみました。

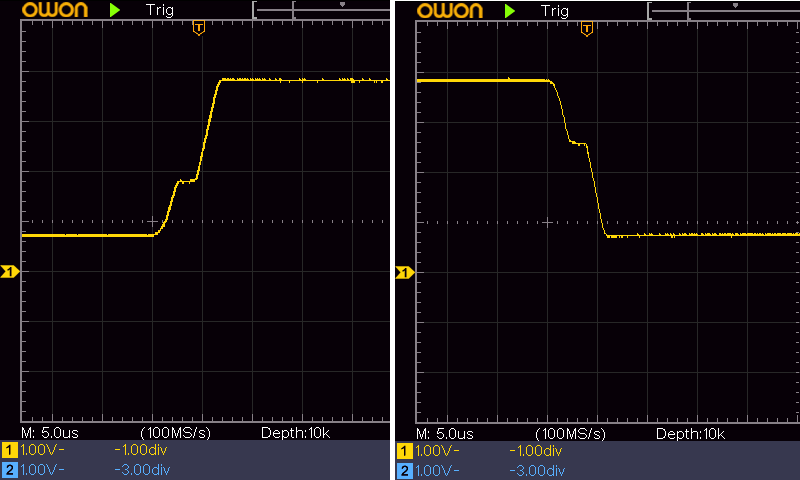

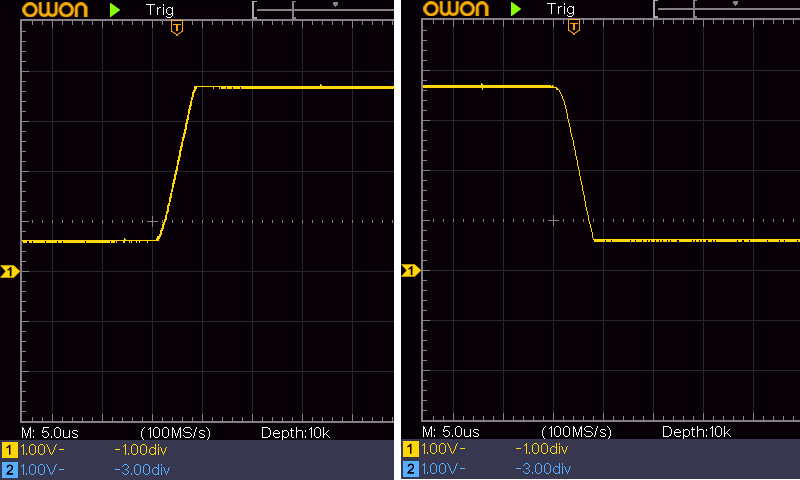

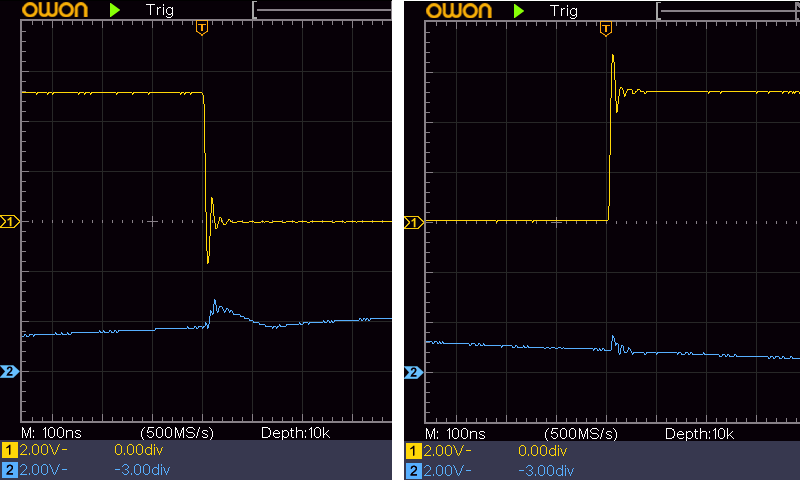

図 (6) の左側は、矩形波の立ち上がり部分、右は立ち下がり部分です。

途中に踊り場のような段があり、立ち上がり時間は 7μs 、立ち下がりも 6μs となっています。通常、C-MOS の入力遷移時間は 400ns 以下ですから、遅すぎます。

矩形波の LOW レベルが 0.7V になっています。シフトレジスタは TTL でしたので、ギリギリです。これもうまくいかなかった原因でしょうか。

波形の段は、オペアンプの出力に負荷抵抗を付けて、電流を流してやるとなくなります。

1KΩ の負荷抵抗を付けたときの波形が、図 (7) です。段がなくなり、立ち上がり、立ち下がりともに 4μs になりました。

ただし、周期 0.82ms 、デューティー比 61% に変化してしまいました。

シュミットトリガ回路を追加する

矩形波の遷移時間が長いと、後段の入力のしきい値で波形がバタついてしまいます。遷移時間を短くして波形を整えるために、シュミットトリガ回路を入れることにしましょう。

図 (8) が、シュミットトリガ回路を追加した回路図です。

オペアンプの負荷抵抗として、R5 を追加しています。

シュミットトリガは、遷移時間の長い信号を安定して入力するために、ヒステリシス特性をもった論理回路です。

毎度のジャンク品 74VHCT14A を使っています。

えーと、秋月電子通商にある 74HC14 でいけるかどうかは?です。試してません。

74VHCT14A は、入力が TTL レベルで、しきい値は VP=1.9V VN=0.5V (Vcc=4.5V) です。VN がちょっと際どいなぁ。レベルシフトダイオードを入れたほうがよいかも。

74HC14 は、入力が C-MOS レベルなので、HIGH レベルは 3.5V 以上。オペアンプの出力電圧がきついです。しきい値は VP=2.7V VN=1.6V (Vcc=4.5V) ですので、なんとかなるっしょ。

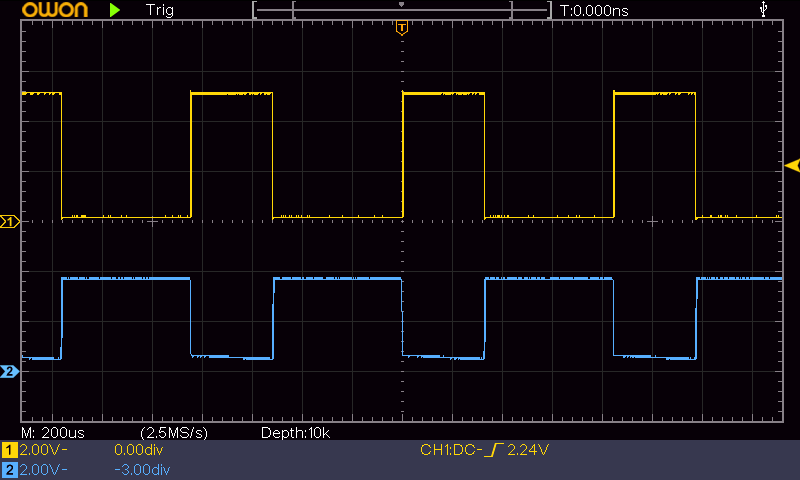

図 (9) が、シュミットトリガ回路の入力 (下) と出力 (上) の波形です。

HIGH レベルは電源電圧、LOW レベルは 0V となりました。

立ち上がり、立ち下がり部分を見てみましょう。図 (10) です。

左は入力の立ち上がり部分です。しきい値 1.8V で入力が HIGH と認識され、出力が LOW になっています。

右は入力の立ち下がりで、しきい値 0.9V で LOW と認識され、出力が HIGH になります。

遷移時間はどちらも 20ns 以下になりました。

出力がオーバーシュート (アンダーシュート) しています。

オーバーシュートすると電源電圧が振動します。それが発振回路に影響して、入力信号も振動してしまっています。

影響が大きいとここで寄生発振してしまうので、出力側にダンピング抵抗入れるとか、コンデンサ入れるとかするとよいと思います。

発振周波数を変えてみた

| R4 | C1 | 周期 |

| 470KΩ | 10μF | 7.9s |

| 100KΩ | 10μF | 1.2s |

| 47KΩ | 10μF | 660ms |

| 10KΩ | 10μF | 210ms |

| 4.7KΩ | 10μF | 65ms |

| 4.7KΩ | 1μF | 6.8ms |

| 4.7KΩ | 0.1μF | 0.84ms |

| 4.7KΩ | 0.01μF | 97μs |

| 4.7KΩ | 1000pF | 17μs |

| 4.7KΩ | 470pF | 10μs |

表 (1) は、抵抗 R4 とコンデンサ C1 の値を変化させたときの発振周期を調べたものです。シュミットトリガ回路の出力を計測しました。

C1 を 100pF にすると、オペアンプのスルーレートが追いつかなくなり、発振しませんでした。このあたりが限界のようです。

発振精度は?です。コンデンサを指でつまむと周期が変化します。温度変化でふらつきます。フィルムコンデンサとかだと、少し安定するかも、です。

まぁ、精度を要求するようなものでは、ないですよねぇ。

シュミットトリガ回路は必須でしょ

今回は、オペアンプを使った矩形波発振回路を試してみました。

オペアンプのスループットが低いので、波形はいまいちです。出力にシュミットトリガ回路は必須だと思いますが、ゆる〜くパルスを利用するなら、そのまま使えるかもしれませんね。