今回は、前回作った SPIコントローラに受信回路を、SPIペリフェラルに送信回路を、それぞれ追加しました。

前回作ったのは、送信回路だけの SPIコントローラでした。

でも、やっぱり受信回路もないとダメだよねぇ。たとえば、コントローラからコマンドを送って、ペリフェラルからレスポンスを受けとるといったような動作をさせるために。

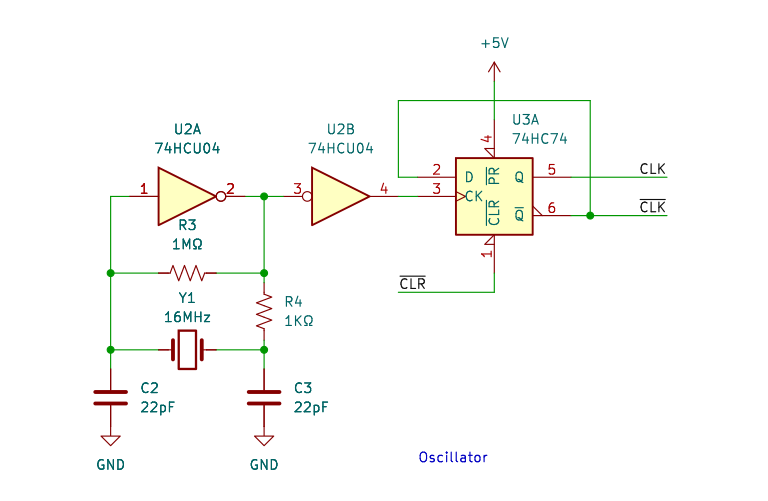

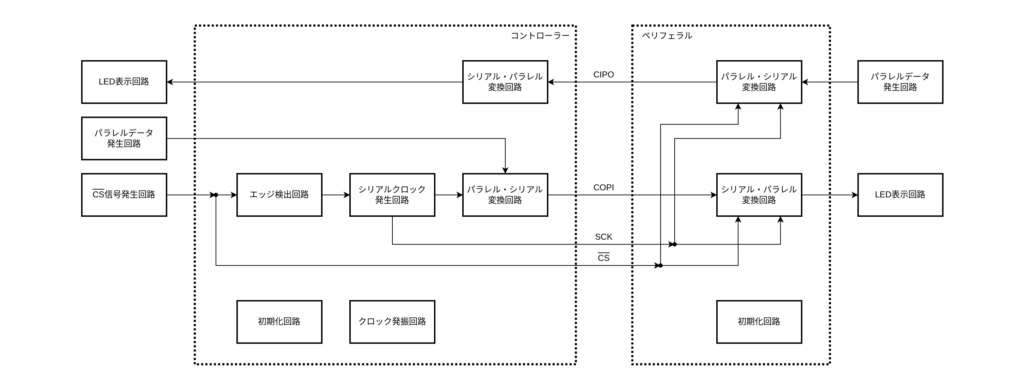

ブロックダイヤグラム

ブロックダイヤグラムです。変更点以外に関しては前回の記事を参照してください。

コントローラに受信回路 (シリアル・パラレル変換回路) とテスト用の LED表示回路を追加しました。

ペリフェラルのブロック図を追加しました。コントローラより、チップセレクト信号 CS、シリアルクロック SCK、シリアルデータ COPI を受けとり、シリアルデータ CIPO を返します。ペリフェラルにもテスト用の回路としてパラレルデータ発生回路、LED表示回路をつくります。

SPIコントローラ回路

各部の回路図です。変更点以外に関しては前回の記事を参照してください。

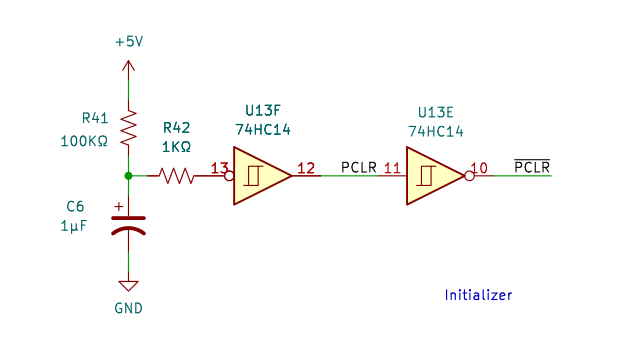

初期化回路

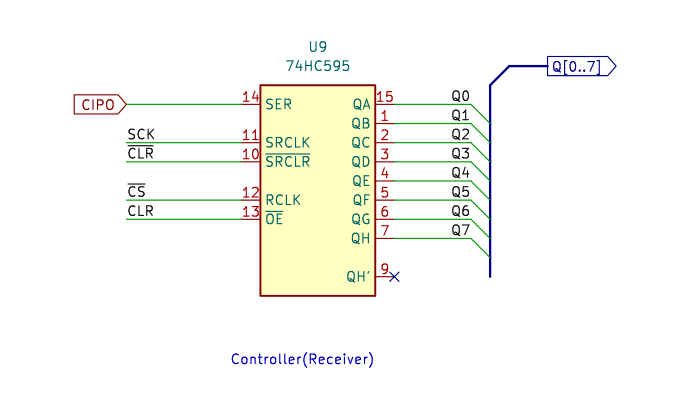

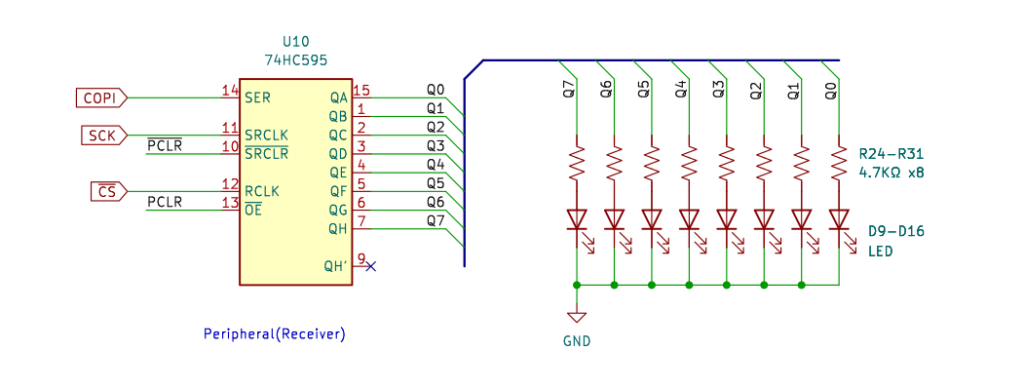

受信回路 (シリアル・パラレル変換)

ペリフェラルから返されるシリアルデータを受けとり、ストレージレジスタ 74HC595 でパラレルデータに変換します。

シフトレジスタクリア SRCLR に負の初期化信号 CLR を、出力イネーブル OE に 正の初期化信号 CLR を入力しています。これにより、電源オン時の無用な出力を抑止します。

電源オン時に、CLR がシフトレジスタを初期化し、その間の出力を CLR で無効にしています。本来ならば、さらにレジスタクロック RCLK を入れてストレージレジスタも初期化してやるべきなのですが、そこまでしなくても無用な出力は抑えられているようです。

74HC595 の初期化については下記の記事を参照ください。

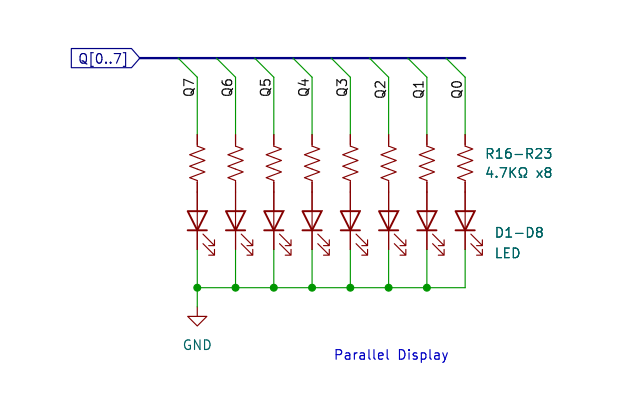

受信データ表示回路

受信した 8ビットのパラレルデータを LED表示する、テスト用の回路です。

74HC595 の出力電圧は 4.5Vなので、LED電流は 0.5mA です。高輝度LED ならば十分な電流です。

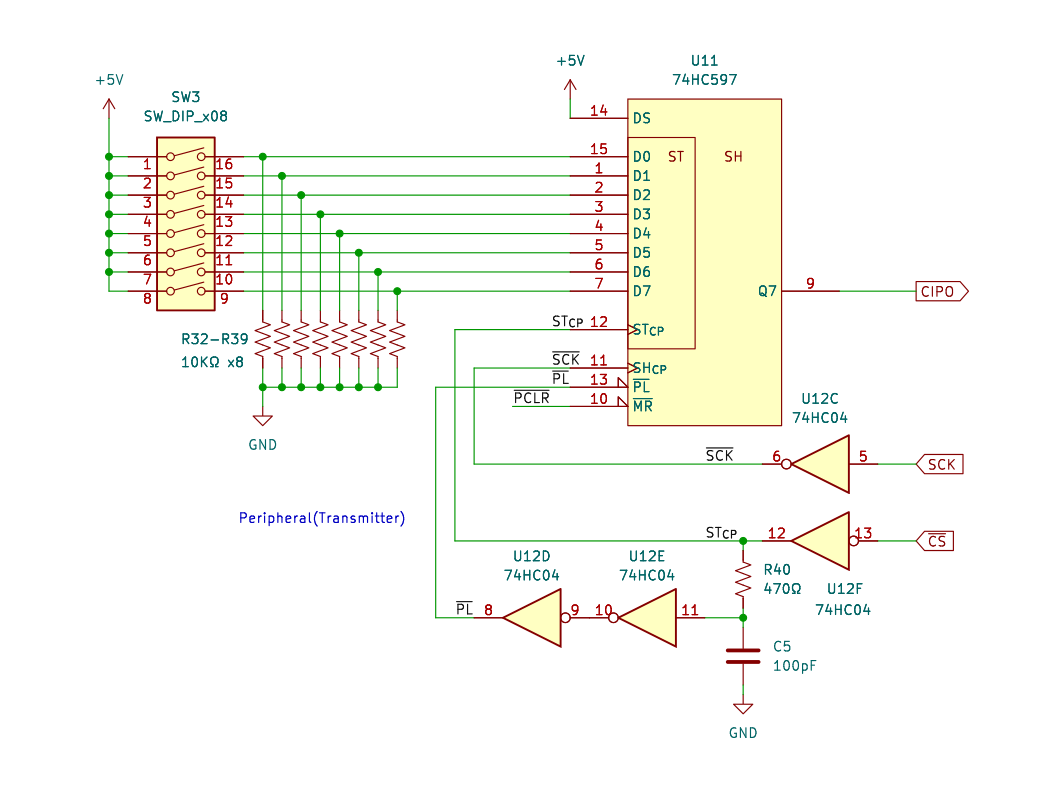

SPIペリフェラル回路

前回はテスト用にと考えていたペリフェラル回路ですが、今回はもう少しちゃんと考えましょう。

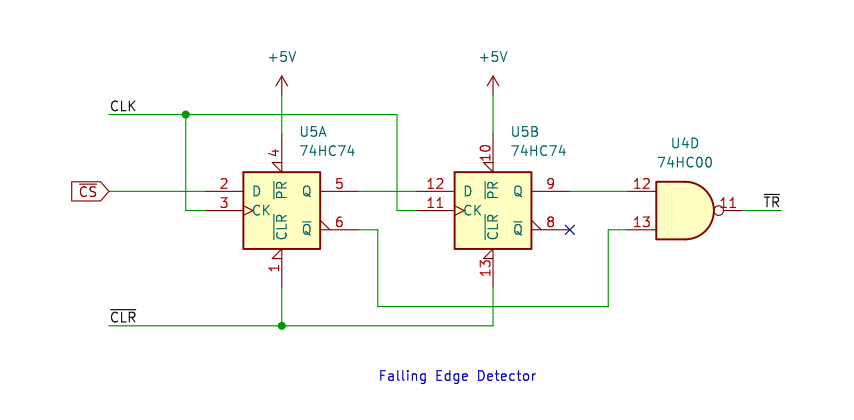

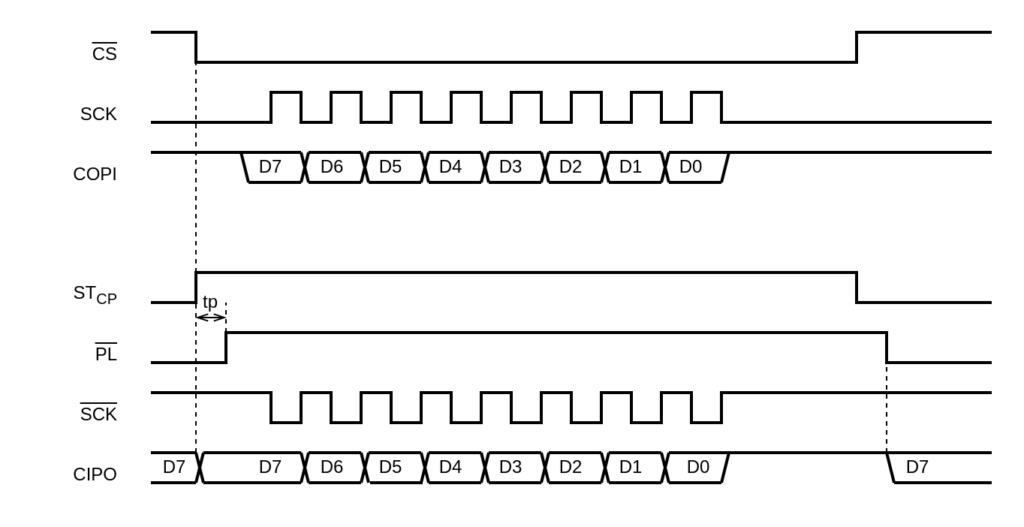

タイミングダイヤグラム

コントローラからチップセレクト信号 CS とシリアルクロック SCK を受けとります。シリアルデータ COPI は、SCK の立ち上がりエッジでシフトレジスタ 74HC595 へ読み込みます (SPIモード 0)。これは、前回のペリフェラル回路での受信と同じです。

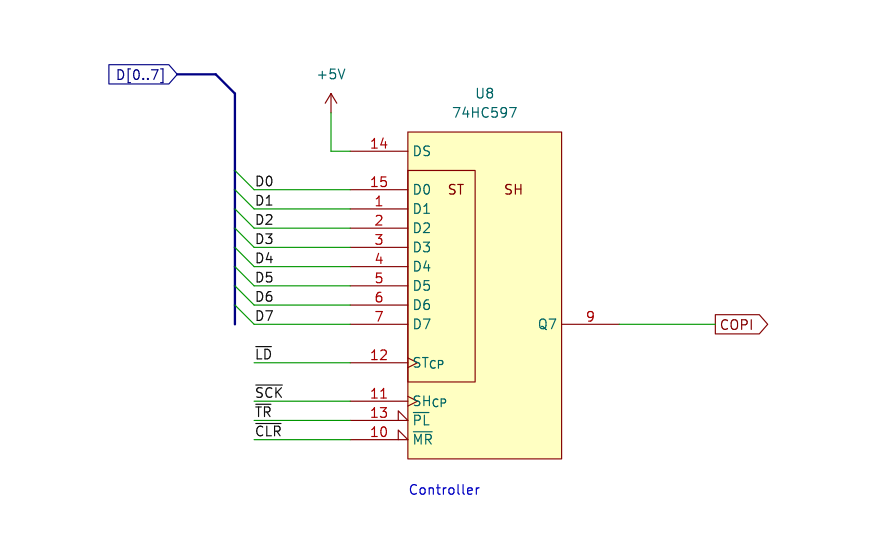

ペリフェラル回路からの送信は、シフトレジスタ 74HC597 で行ないます。

入力されたパラレルデータは、CS を反転したストレージクロック STCP でストレージレジスタへ読み込みます。さらに、STCP を tp だけ遅延した信号をパラレルロード PL としてシフトレジスタを起動します。STCP が立ち上がるとき PL は LOW ですので、入力データはストレージレジスタと同時にシフトレジスタへも送られます。

データの送出はシリアルクロック SCK の立ち下がりエッジで行ないます (SPIモード 0) ので、SCK を反転した SCK でデータシフトし、シリアルデータ CIPO とします。コントローラでは、SCK の立ち上がりエッジでデータを読み込みます。この動作タイミングは、コントローラ側の送信動作と同じです。

なお、送信終了後に PL が LOW になると入力データ D7 を読み込みますので、待機中の CIPO の位相は D7 の影響を受けます。D7 の値は、STCP の立ち上がりエッジで読み直されます。

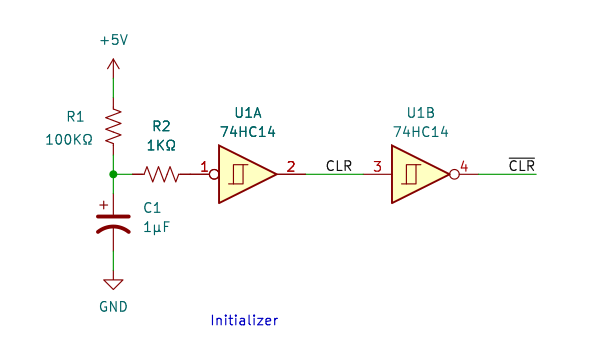

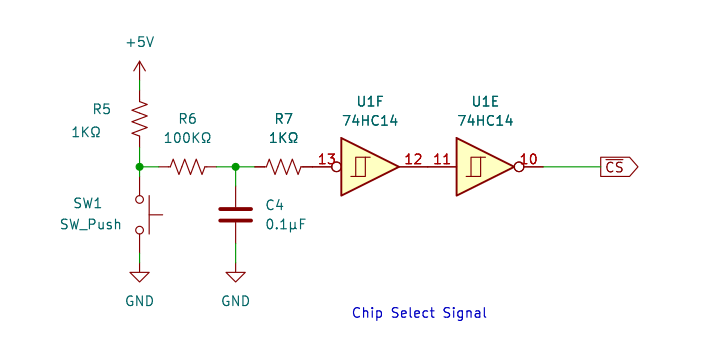

初期化回路

いつもの初期化回路です。ペリフェラル回路用に別途つくります。

後述の送信回路にインバータ 74HC04 を使っているので、それを利用してもよいのですが、通常のインバータではどうしても発振しやすくなります。ここはやっぱりシュミットトリガインバータ 74HC14 を使いましょう。

受信回路 (シリアル・パラレル変換)

コントローラから送られたシリアルデータを受けとり、ストレージレジスタ 74HC595 でパラレルデータに変換します。データ表示用の LED回路も含めてあります。入力されるシリアルデータが COPI であること以外は、コントローラの受信回路と同じです。

ペリフェラルの初期化回路から初期化信号を入れています。この動作もコントローラと同じです。

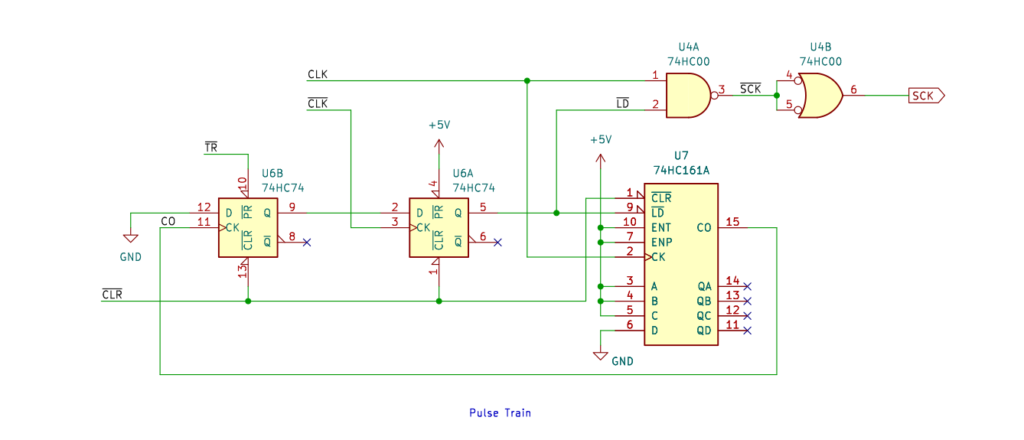

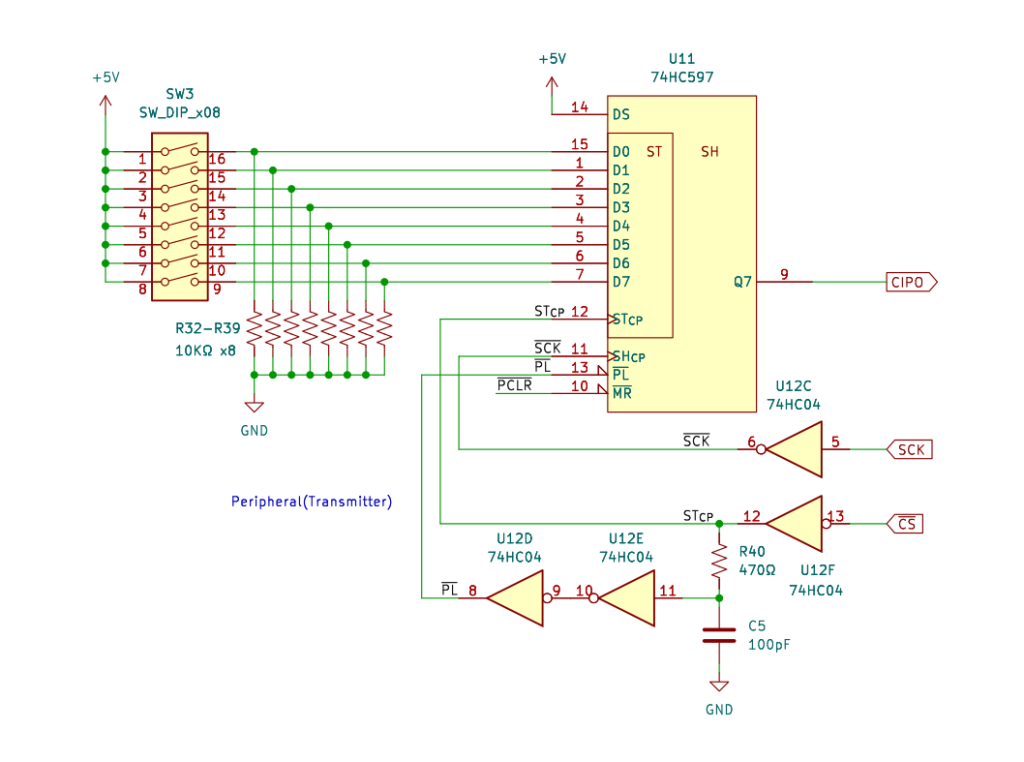

送信回路 (パラレル・シリアル変換)

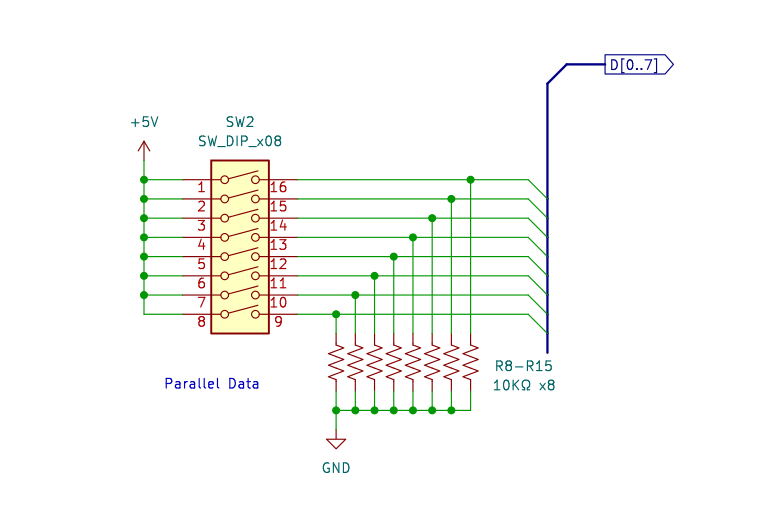

Dipスイッチで発生させた 8ビットパラレルデータを、シフトレジスタ 74HC597 でシリアルデータに変換し、CIPO としてコントローラへ送ります。基本的な動作はコントローラと同じです。

シフトレジスタの制御信号は、チップセレクト信号 CS を反転した信号をストレージクロック STCP として、STCP を遅延したものをパラレルロード PL として入力します。PL が LOW の状態で STCP を立ち上げることで、入力データをシフトレジスタへ送ります。PL が HIGH になるとシフト動作が始まります。

遅延回路は、インバータ 2段だけでもいけそうですが、余裕をみて CR 回路を加えました。CS からの遅延時間 tp は 80ns です。CS から最初のシリアルクロック SCK の立ち上がりまでは最小 125ns ですので、シフト動作に影響はありません。

シフト動作はシリアルクロック SCK の立ち下がりエッジで行ないます (SPIモード 0) ので、シフトクロック SHCP は SCK を反転させた SCK を入力します。コントローラでは SCK の立ち上がりエッジでデータを読み込みます。

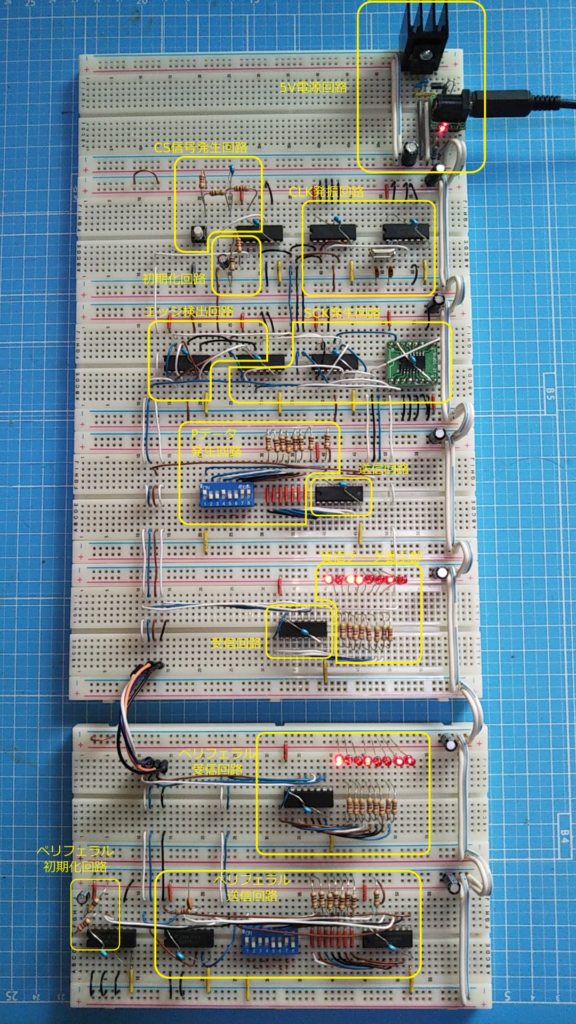

ブレッドボード

ペリフェラルからの信号 CIPO を受信できるようにした回路のブレッドボードです。

コントローラは、送信回路 (P-S変換回路) までは変更ありません。その下に CIPO の受信回路 (S-P変換回路) と LED表示回路を追加しています。

ペリフェラルの上側のブレッドボードが受信回路の 74HC595 と LED表示回路です。

下側が送信回路で、左から初期化回路 74HC14、遅延回路 74HC04、データ発生用のDipスイッチ、パラレルシリアル変換の 74HC597 と並んでいます。

CS 信号用のタクトスイッチを押下すると、コントローラのデータがペリフェラルに、ペリフェラルのデータがコントローラに、それぞれ交換されることを確認しました。

ちなみに、いつもの調子で回路をズラズラと並べましたが、発振回路のノイズがかなりでますね。発振回路は分離するようにしたほうが良さそうです。

後記

今回は、ペリフェラルと送受信ができる SPIコントローラを、ロジックIC を使って試作してみました。

SPI通信について、勉強を始めたのはこの記事からです。

当初、SPI通信についてググってみたものの、概要はなんとなくわかるけど詳細がチンプンカンプン。SPI_MODEがぁ、CPOLがぁ、CPHAがぁ、なんのこっちゃ?

今回の試作で扱ったのは SPI_MODE0 のみです。このモードは、クロックの立ち下がりエッジでデータを送出 (シフト) し、立ち上がりエッジで読み込みます。同様に、SPI_MODE1 では立ち上がりで送出し、立ち下がりで読み込む。それだけの話です。

SPI_MODE2 と SPI_MODE3 はクロックが負理論に変わります。これもそれだけの話。

なんていうかなぁ、さまざまある技術解説は難しすぎる。難しすぎて、俺みたいな悪い頭にストンと落ちてこない。そんな難しい話を理解するのに、この試作はとても役立ってくれました。たぶん、1週間もしたら忘れますけど (;´Д`)、きっと備忘録になってくれるでしょう。