オペアンプを使った矩形波発振回路について、過去に一度試してみたことがあります。このときは、発振回路を試しつつ、購入したオシロスコープで発振波形をみてみようということが主眼でした。

今回は、もうちょっとこの発振回路について確認してみようと思います。

なお、もっともらしい計算などしてますが、まいどのごとく、俺の計算はテキトーです m(_ _;)m

オペアンプの準備

余談なんですけど、ちょっとした Tips を。

使用したオペアンプは、汎用オペアンプ LM324 です。汎用オペアンプなら、なんでもいいです。部品箱にあるものをテキトーに。

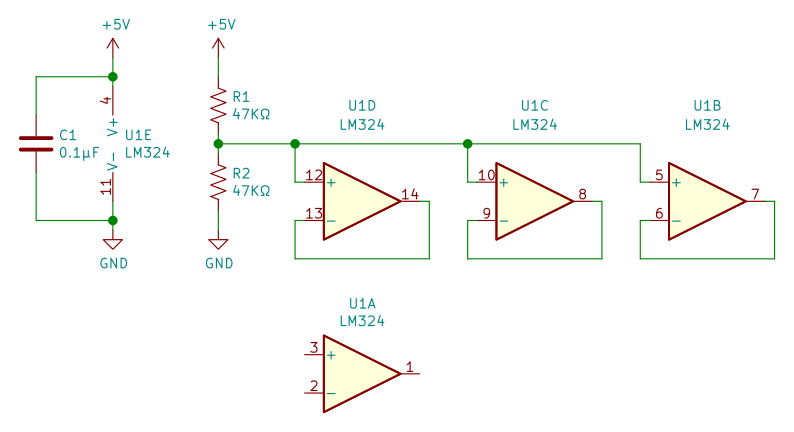

LM324 には、オペアンプが 4個入っています。今回使うのは U1A の 1個だけですが、他の 3個を放置するのは避けましょう。

未使用端子は図1 のようにしておきます。オペアンプは、出力をー入力につないだボルテージフォロワとします。+入力には、電源電圧の半分ほどの電圧を加えます。

また、電源端子にはパスコンとして 0.1μFほどのコンデンサをつないでおきましょう。

準備ができたら、発振回路をつくります。

矩形波発振回路

発振回路の動作のよくある解説

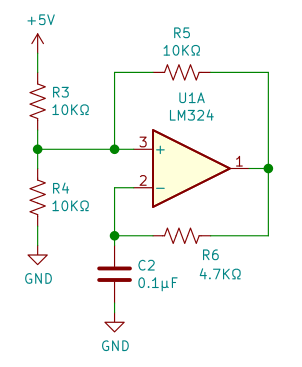

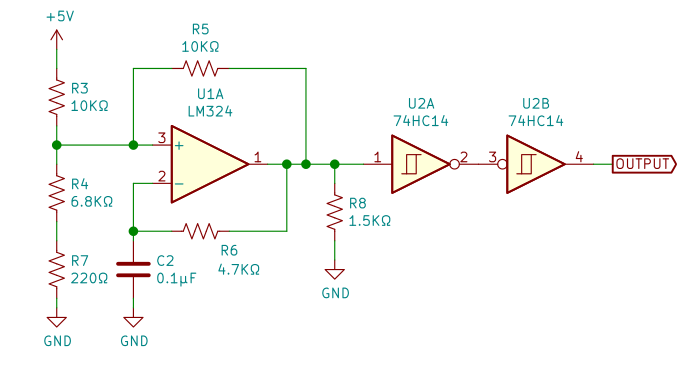

図2 が矩形波発振回路。ググるとよくみかける、一般的なオペアンプによる発振回路です。

R3、R4、R5 で構成されるのは、ヒステリシス特性のあるコンパレータ回路です。+入力とー入力の電圧を比較し、+入力の電圧が高ければ出力は HIGH になります。

3つの抵抗で 5Vを分圧しています。出力が HIGH のとき+入力の電圧は 5Vの 2/3 の 3.33V、LOW のとき 1/3 の 1.67Vとなります。

R6 と C2 が RC回路で、この回路の時定数で発振します。

出力が HIGH のとき、R6 をとおして C2 が充電される。コンデンサの電圧が 3.33Vを超えると出力は LOW になる。するとコンデンサは放電しはじめ、1.67Vを下回ると出力は再び HIGH になる。こうして矩形波を発振するというしくみです。

発振周期 T は、

T = 1.39⋅C2⋅R6 = 1.39 x 0.1 x 10-6 x 4.7 x 103 = 0.65 [ms]

周波数にすると、1.53KHz です。

と、ここまではよくある一般的な解説です。が、じっさいの回路では少し違うようです。

じっさいの発振回路の動き

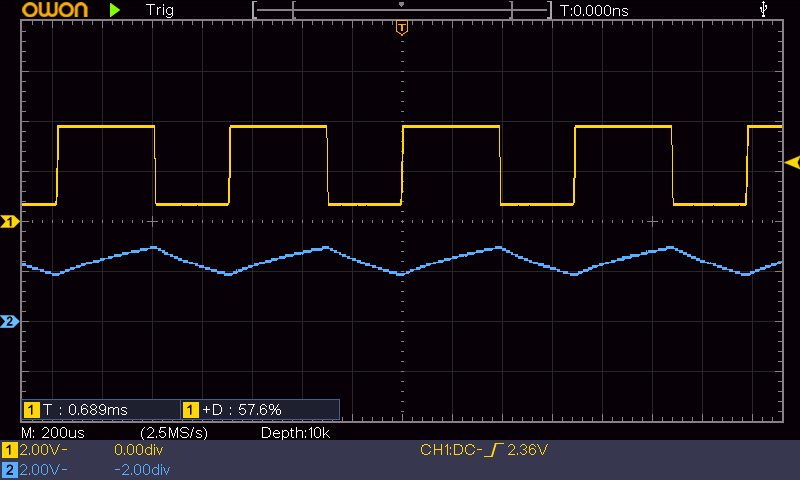

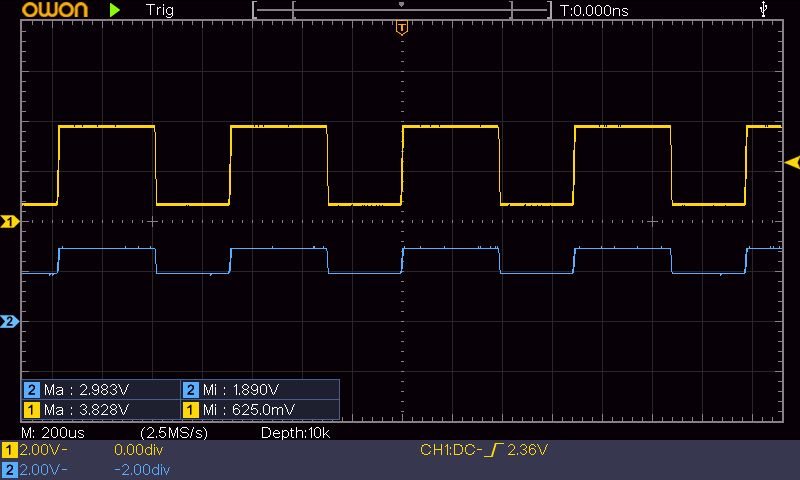

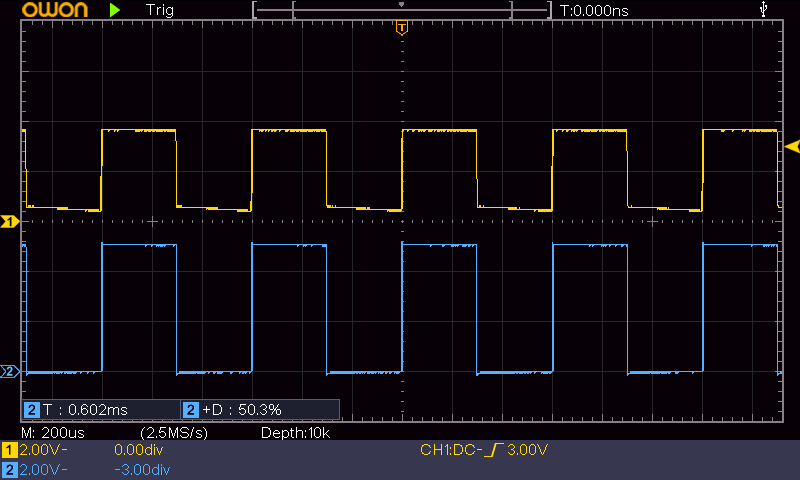

図3 は、オペアンプの出力電圧 (黄) とコンデンサの電圧 (青) の波形です。

発振周期は 0.689ms、周波数では 1.45KHz です。計算値に近くなりましたが、あくまでも近似値計算です。また、定数の誤差や温度などにより変動します。

出力電圧の最大値 (HIGH) は 3.83V、最小値 (LOW) は0.63V です。+デューティ比は 57.6% と、+側の時間が長くなっています。

コンデンサの電圧の最大値は 3.0V、最小値は 1.9V ほどと読めます。これは、上の解説によれば 3.33V と 1.67V になるはずですが、わりとずれています。

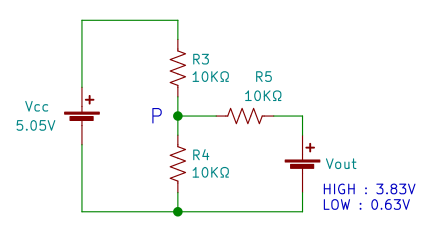

図4 は、コンパレータの基準電圧となる+入力の電圧波形 (青) です。解説では、出力が HIGH のとき 3.33V、LOW のとき 1.67V になるはずですが、じっさいは 2.98V と 1.89V です。これは、コンデンサの電圧と同じです。

なお、電圧は異なっていますが、基準電圧でコンデンサの充電と放電が切り換わるという動作には、間違いはありません。

なぜ基準電圧が計算と異なるのか?

答えは簡単です。オペアンプの出力電圧が、電源電圧と等しい 5Vではなく、3.83Vしかないからです。

LM324 のデータシートには、電源電圧が 5Vのときの出力電圧が載っていませんでしたが、同等だと思われる BA10324 では 3.5V (min) となっています。汎用オペアンプの HIGH のときの出力電圧はだいたいそれくらいなので、3.83Vは正常な値でしょう。

実測値から、コンパレータの基準電圧を計算してみましょう。

図5 が、コンパレータの基準電圧を分圧している部分の等価回路です。これより、基準電圧となる P点の電圧を求めます。

キルヒホッフの法則より、

IR4 = IR3 + IR5 Vcc = IR3⋅R3 + IR4⋅R4 Vout = IR5⋅R5 + IR4⋅R4

これを計算すると、Vout=3.83V (HIGH) のとき Vp=2.96V、Vout=0.63V (LOW) のとき Vp=1.89V となり、実測値とほぼ同じになりました。

コンデンサ C2 の電荷は一定なので、充放電時の電圧差が大きいほど電流が大きくなり、速く充放電します。充電時間 tH と放電時間 tL の比が、それぞれの電圧差の比に逆比例するとすれば、

tH:tL = |0.63-2.96|:|3.83-1.89| = 2.33 : 1.94 = 54.6% : 45.4%

となり、+デューティ比が大きくなってしまいます。

デューティ比を 50%にする

では、デューティ比を 50%にするにはどうしたらよいでしょう。

デューティ比を 50%にするには、充電時間と放電時間を同じにする、つまり、充電時と放電時の電圧差を同じにする。そのためには、基準電圧の中心値を、出力電圧の中心値に合わせればよいはずです。

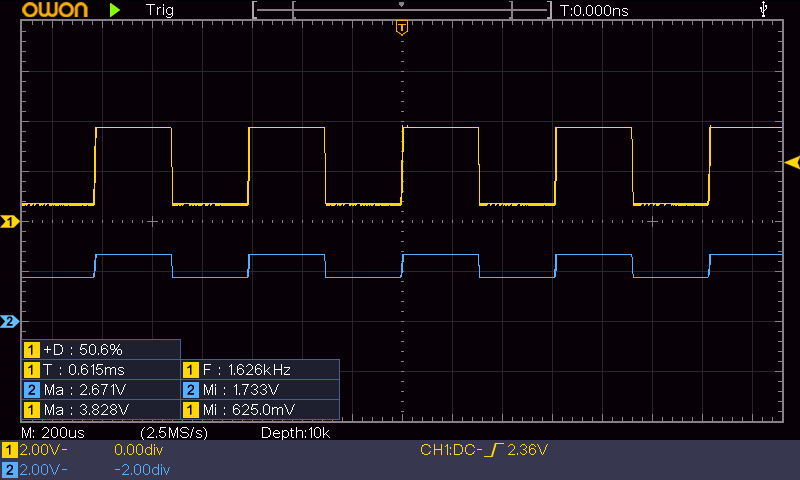

出力電圧の中心値は 2.23Vです。P点の電圧がこれに近づくように、カットアンドトライで R4を 7.8KΩ (6.8KΩ+1kΩ) に替えてみました。そのときの波形が図6 です。

充電時の電圧差が 2.10V、放電時は 2.04Vとほぼ同じになり、デューティ比が 50.6%に改善されました。

発振周期が 0.62msと短くなっています。が、上でやった計算結果に近づきました。

上にでてきた周期の計算式は、R3、R4、R5が等しくて、出力電圧が電源電圧まで上昇するとしたときの式ですので、本来は成り立ちません。正しい計算はむずかしいのでパス。でも、基準電圧を調整したために、実測値が計算値に近づいたようです。

つまり、出力電圧の中心値を基準電圧とし、デューティ比を 50%にすることで、周期計算も近似する、んじゃないかと。

波形の改善

波形の歪み

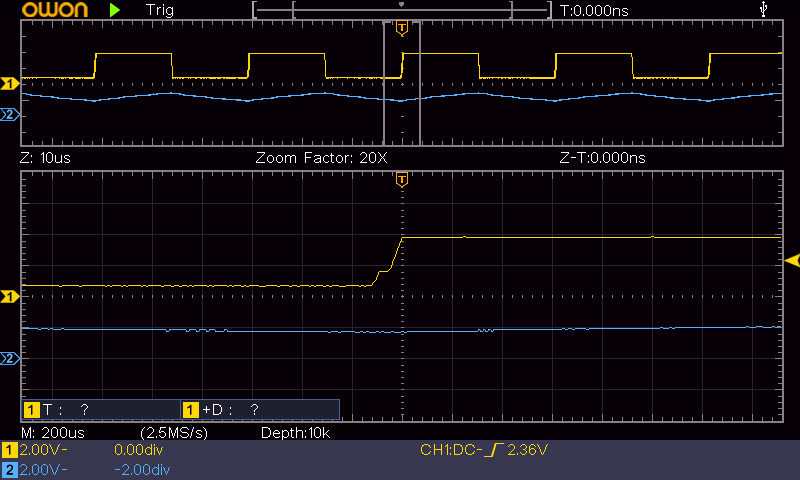

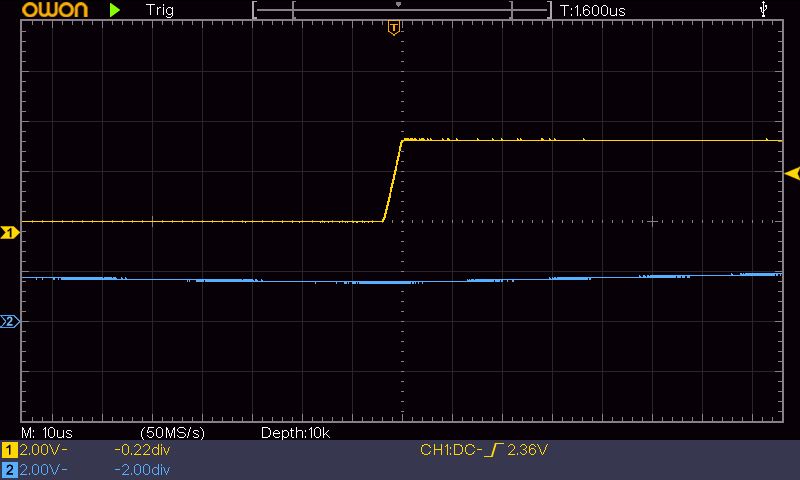

図7 は、矩形波の立ちあがり部分を拡大したもの。黄が出力波形、青がコンデンサの電圧です。

立ち上がりの途中で段ができています。これは、立ち下がり部分にも発生しています。

ちょうどコンデンサの電圧と出力電圧が交差するときに、出力が一服してしまうようです。

これについては、出力に負荷抵抗として 1.5KΩを追加することで改善しました。

理由はよくわかりません(*1)。が、オペアンプをコンパレータとして使用すると応答性がとても悪いので、その影響とかあるのかな?と。オペアンプの場合には、それなりに電流を流してやる必要がある、ってことでしょうか。

コンパレータは正帰還回路です。正帰還動作のばあい、Vin+≠Vin- では飽和状態となり出力が HIGH または LOW になります。でも、Vin+=Vin- のときは平衡状態となり、Vo=Vin+ の段ができるのではないかと。出力電流を流してやると平衡が崩れやすくなり、段をつくらずに飽和する。ということではないかと思います。

なお、負荷抵抗をつけると出力電圧が下がる (実測値 3.67V) ので、+デューティ比が大きくなってしまいます。R4 を 7.02KΩ (6.8KΩ+220Ω) に調整しました。

立ち上がり時間

図8 は、矩形波の立ち上がり部分です。負荷抵抗をつけたので、段はなくなっています。

立ち上がり時間は約 4μs、立ち下がりも同様です。

さて、この矩形波を、たとえば論理回路のクロックとして利用しようとすると、どうでしょうか。

たとえば 74HCシリーズでは、必要な入力の立ち上がり時間は 500ns/V ぐらい、5Vならば 2.5μsより短くないといけません。オペアンプの出力をそのまま利用しようとすると、誤動作してしまいます。

また、CMOS の入力レベルは Vccの 0.2~0.7 倍ですから、5Vならば LOW が 1.0V、HIGH が 3.5V です。オペアンプの HIGH 出力が 3.5Vだとすると、これも誤動作の原因になります。

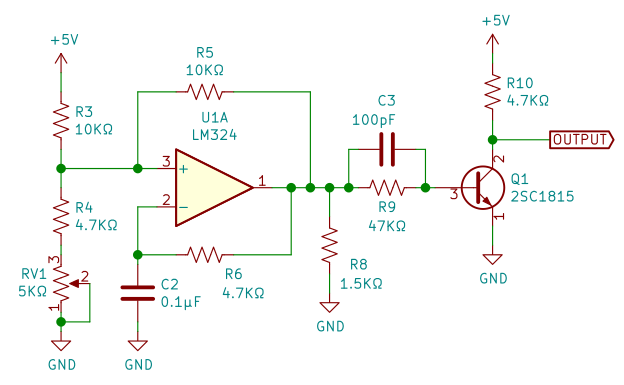

シュミットトリガを追加する

波形を改善するのに有効な方法は、シュミットトリガの追加です。74HC14 を使ってみましょう。

でも、74HC14 は CMOS なので入力電圧が気になります。今回は、オペアンプの出力電圧が 3.67Vなのでなんとかなりそうです。このあたりは個体によるでしょうから、場合によっては誤動作するかもしれません。誤動作するようであれば、トランジスタでも使って 5Vにレベルシフトすればよいと思います。

レールツーレール出力のオペアンプ使えって? それが部品箱にあるなら、ね (;´Д`)

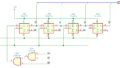

シュミットトリガを追加した回路が図9 です。これまでの定数の変更なども反映してあります。

シュミットトリガインバータは 2段つないでいます。これは定石です。

なぜに定石か?わかりませんけど、まぁ正理論にもどすといった程度のことではないでしょうか。1段だとデューティ比が変化するってのもあるかもしれませんが、わずかな話です。

ちなみに、74HC14 は 6回路入りですので、未使用回路の処理をしておきましょう。使っていない入力端子は 5Vまたは GNDにつないでおきます。出力はオープンのままです。また、電源にはパスコンを入れます。これらも定石です。

図10 は、シュミットトリガの出力波形 (青) です。電圧は 0-5V、立ち上がり時間は 10ns以下になりました。いまのところ誤動作は確認していません。

最終的に、周期 0.60ms、周波数 1.67KHzになりました。デューティ比もほぼ 50%です。クロックとしてじゅうぶん利用できると思います。

後記

今回は、オペアンプを使った矩形波発振回路の動作などを確認してみました。

オペアンプについては、あまり知識があるわけでもありませんし、まいどのテキトーな計算しかしないので、内容についての保証なんてできません。やってみたらこうなったレベルですので、ご容赦を。

でもまぁ、オペアンプの出力レベルとか負荷抵抗とか、シュミットトリガは必須じゃね?とか、じっさいにこの回路を使うときに留意しておきたいことは記録できたかなと、思ってます。

そうだ、どうしてデューティ比を 50%にしたいか、って話。

たとえば、ここで発振した矩形波を積分して三角波にして PWM波にしようなんてときに、デューティ比が50%から大きく外れてると積分やりにくい、とか。論理回路の同期クロックとして利用するとき、デューティ比が 50%じゃないクロックを反転させちゃうと同期がくるっちゃう、とか。

クロックパルスは、できるだけデューティ比 50%になっているほうが扱いやすいんです。たぶんね。