以前試してみたシフトレジスタは、シリアル入力パラレル出力 (SIPO) タイプでした。

今回は、パラレル入力シリアル出力 (Parallel-In, Serial-Out, PISO) タイプのシフトレジスタをつくってみましょう。

ちなみに、PISOでは入力が複数ありますが、最初の入力だけを使うとシリアル入力にできます。また、各段のフリップフロップから出力させるとパラレル出力です。つまり、PISOも SIPOもできちゃうし、さらには SISOも PIPOもできる、汎用なシフトレジスタということです。

実験のための周辺回路

まずは、毎度のように、実験するために必要な周辺の回路をつくっておきます。

電源は DC+5V です。電源回路は描いていませんが、適当に用意してください。また、空き端子の処理とか、電源のパスコンとか、回路図に描いてなくてもあたりまえにやってください。

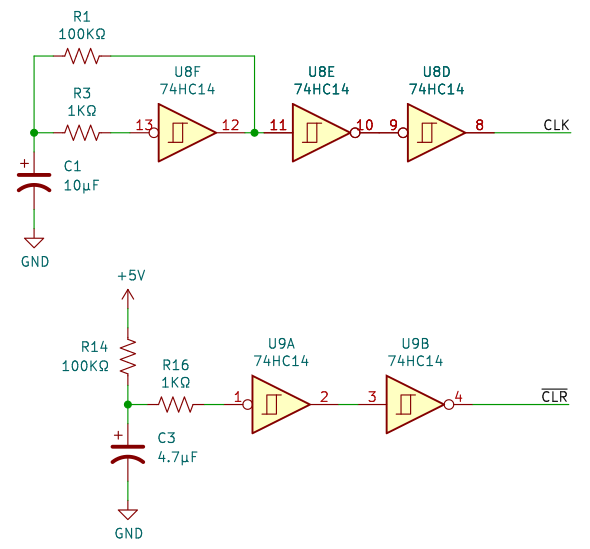

クロック発振回路・初期化回路

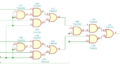

図1 上は、クロック発振回路です。

いつも使っているシュミットトリガインバータ 74HC14の矩形波発振回路。発振周波数は 1Hzほどです。(参考記事)

図1 下は、電源オン時の初期化回路。これも毎度まいどの回路です。

フリップフロップは電源オン時の状態が不定です。電源オン時に、一時的に CLR を LOW にすることで、フリップフロップの出力を LOW に初期化します。

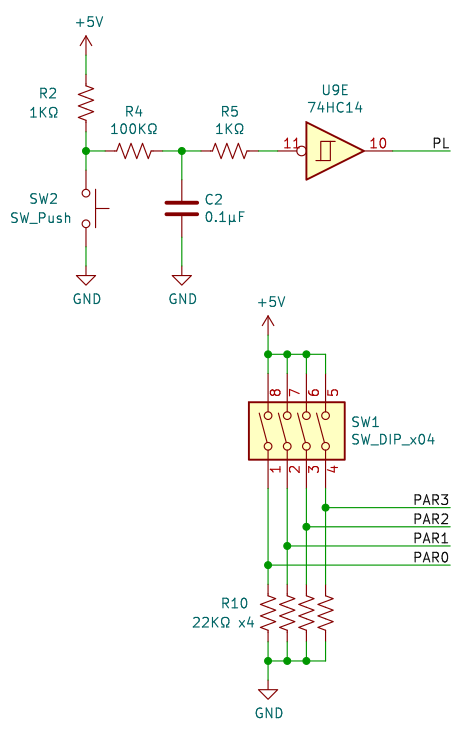

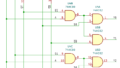

パラレル信号ロード回路

図2 上は、パラレル信号をロードさせるための押しボタンスイッチ回路です。

R4、C2のローパスフィルタとシュミットトリガインバータ 74HC14は、押しボタンスイッチのチャタリング防止回路。R2はプルアップ抵抗、R5は保護抵抗です。

ちなみに、ネットでは、R2 を大きくしている回路をよくみるのですが、スイッチに流す電流が小さいと接触不良を起こしやすいので、それなりに電流を大きくしておくほうが吉です。

図2 下は、入力するパラレル信号を発生させる Dipスイッチ。4ビットのビット列を出力します。Dipスイッチをオンにすると 1、オフにすると 0 です。

4本の抵抗 (R10) はプルダウン抵抗です。

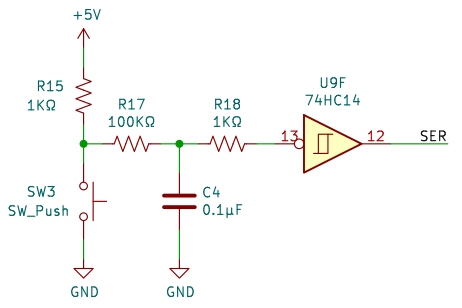

シリアル信号回路

シリアル信号を出力するための押しボタンスイッチ回路です。図2 の押しボタンスイッチ回路とまったく同じ、押しボタンスイッチとチャタリング防止回路です。

パラレル入力を試すので必要ないっちゃ必要ないんですけど、せっかくなのでシリアル入力も試せるようにしておきたいなということで、つくっておきました。

必要なければ、シフトレジスタの SER 入力は GND に落としておきましょう。

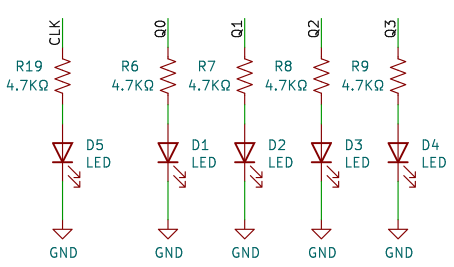

LED表示回路

D1~D4 が、出力状態を表示させるための LED です。

それぞれが各フリップフロップの出力をパラレルに表示しますが、最終段の出力 D4 が、目的のシリアル出力ということになります。

D5 はクロックの表示です。

ちなみに、LED に流す電流は 0.6mA ほど。秋月電子通商で購入した 100個入り数100円の赤色LED ですが、この程度の電流で十分です。10~20mA も流したら、眩しくてみてられませんから。

シフトレジスタ回路 (パラレル入力・シリアル出力)

周辺回路ができたので、本題のシフトレジスタをつくりましょう。

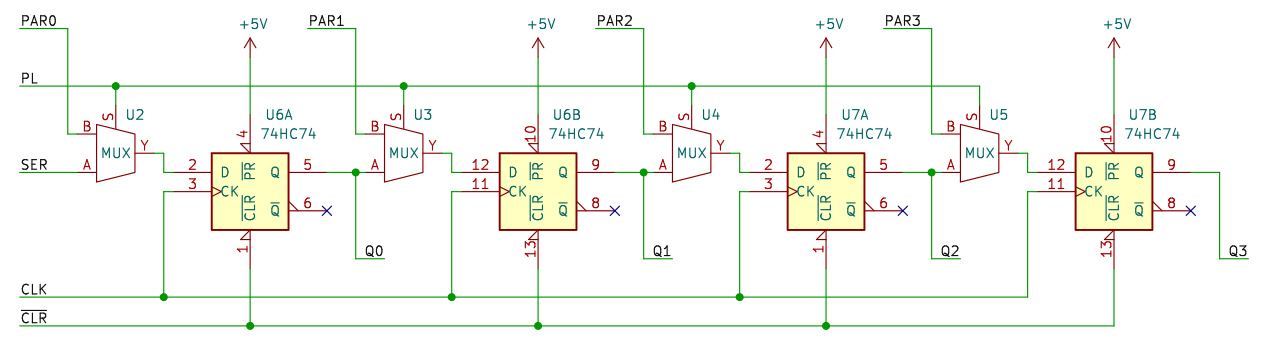

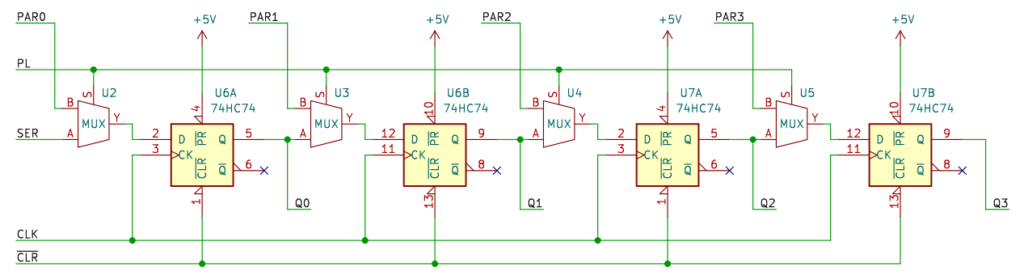

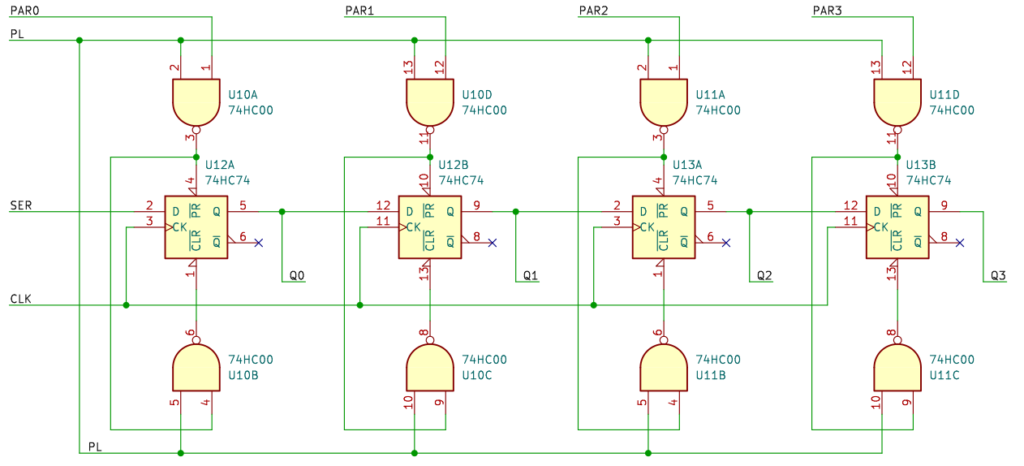

シフトレジスタ回路

MUX はマルチプレクサ (参考記事) です。

パラレル信号ロード PL が HIGH になると、パラレル入力 PAR0~PAR3 が選択され、各段のフリップフロップに入力されます。PL が LOW ならば、初段フリップフロップに入力されたシリアル信号 SER が、順に次のフリップフロップに渡される。

そんな感じの回路です。

PL が LOW のとき (シリアル入力)

パラレル信号ロード PL が LOW のとき、MUX の入力 A が Y に出力されるので、各フリップフロップは順番につながっている形となり、以前に試した SIPO シフトレジスタ (過去記事) と同じ動作になります。このとき、出力 Q0~Q3 はパラレル出力になります。

前に試したときと同様に、シリアル信号 SER の押しボタンを押下すると、クロックに伴って信号が Q0から Q3へと遷移していくことが確認できました。

PL が HIGH のとき (パラレル入力)

まず、パラレル信号の Dipスイッチを任意の値に、ここでは仮に 0b1100 に、セットします。次に、パラレル信号ロード押しボタン PL を押下する (HIGH) と、PAR0=1、PAR1=1、PAR2=0、PAR3=0 がそれぞれのフリップフロップに入力され、クロックが入ると出力されます。

PL が LOW になると、フリップフロップは順次出力を次段に送り、最終段の Q3 から 0→0→1→1 と信号を吐き出していきます。つまり、入力した 0b1100 というデータが LSB からシリアルに出力された、ということです。

これが、パラレル入力シリアル出力の動作です。

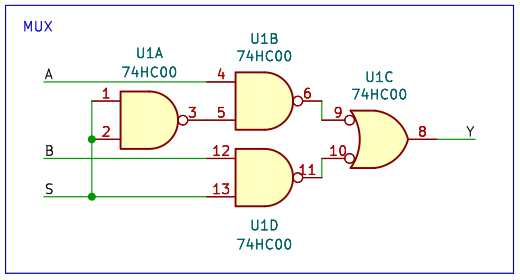

マルチプレクサ (MUX) 回路

回路がわかりにくくなるので、マルチプレクサを MUX として描いていますが、内部は図6 のようにしています。(参考記事)

マルチプレクサ回路の論理式は、

Y = S⋅A + S⋅B

この式を少し変換し、NANDゲートのみで構成して 74HC00 1個で 1回路つくっています。

74HC165 の内部回路を倣う

ここまで、PISO シフトレジスタの回路を試してきました。基本的な動作は理解できたと思います。

理解できたところで、あらためてデータシートをみてみました。

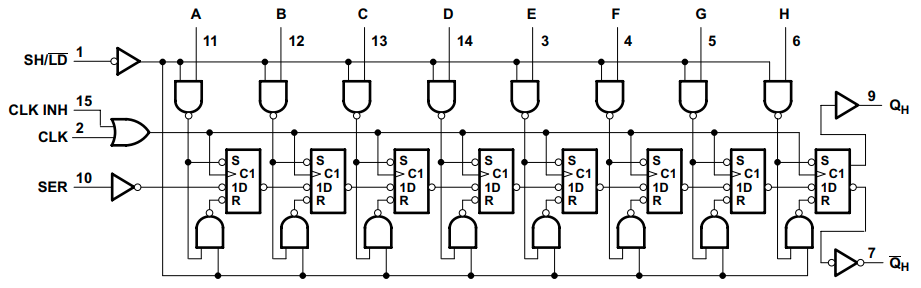

74HC165 内部回路図

PISO シフトレジスタは、74HCシリーズでは 74HC165、74HC166 などが相当します。

内部回路図 (図7) をみてみると、ん?ちょっと回路が異なっていませんか? マルチプレクサは使わずに、フリップフロップの SET、RESET でデータを設定しているようです。

SET/RESET を利用した回路

74HC165 に倣って、パラレル信号ロード PL を HIGH にしたとき、パラレル信号データが 1 ならば SET、0 ならば RESET する、という動作をするように、回路を変更してみました。(図8)

PL が LOW のとき、フリップフロップの PR (SETに相当)、CLR (RESETに相当) はどちらも HIGH(*1) です。シリアル入力 SER は順次、次段のプリップフロップへ送られていきます。

PL が HIGH のとき、パラレル信号が 1 ならば PR が LOW、CLR が HIGH となって出力が 1 に、パラレル信号が 0 ならば PR が HIGH、CLR が LOW となって出力が 0 に設定されます。

この回路も、マルチプレクサを使った回路と同様に動作しました。

なお、この回路では CLR をデータ設定用に使っているため、電源オン時、フリップフロップが不定になります。電源オン時に出力を 0 にセットするための初期化信号を入れようとすると、OR ゲートがフリップフロップの段数分必要になります。

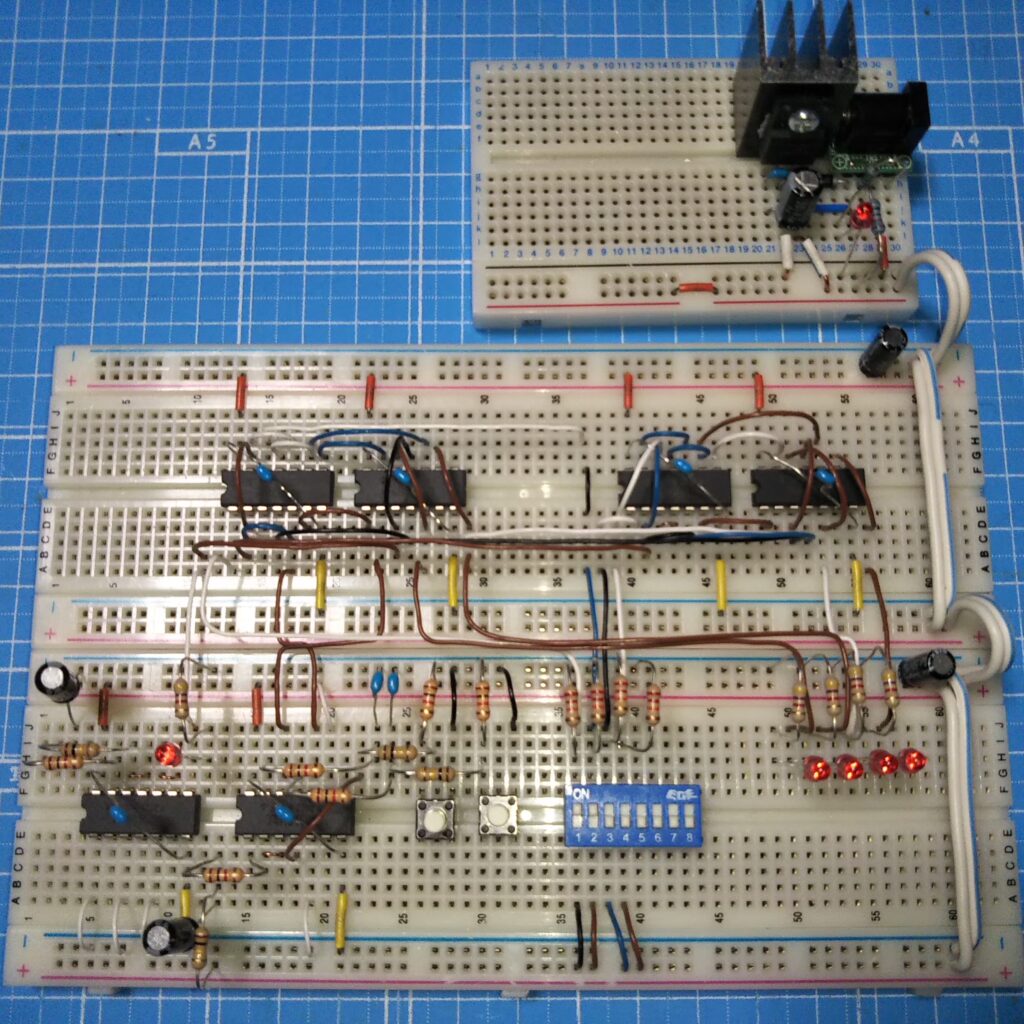

ブレッドボード

後記

今回は、パラレル入力シリアル出力 (PISO) のシフトレジスタを試してみました。

SIPO のシフトレジスタは、Arduinoの出力ピンを増やすために使われることがあります。同様に、PISO のシフトレジスタでは、入力ピンを増やすことが可能です。そこまで必要か?って疑問はありますけど。

品番は、74HCシリーズでは、

74HC165、74HC166

74HC597、74HC7597

といったところがあるようですが、秋月電子通商には 74HC165 しかありませんでした。(2023.7.25 現在)

74HC165 はパラレル信号ロードが非同期、74HC166 はクロックに同期します。74HC597 は、入力フリップフロップ付きで同期、74HC7597 も入力フリップフロップ付きですが非同期となっているようです。選定時には、あらためて仕様を確認しましょう。