一定の数のパルス列を出力するパルストレイン発生回路をつくります。

一般にパルストレイン (pulse train) とはパルス波 (pulse wave) と同義のようですが、ここでは「指定した数だけパルスを出力して停止する」ようなパルス列をパルストレインと呼ぶことにします。いつまでも続く長い列ではなくて、電車のようにいくつかが連なっているというイメージです。

回路をつくるにあたり「機器開発入門 ロジック回路」を参考にさせていただきました。ありがとうございます。

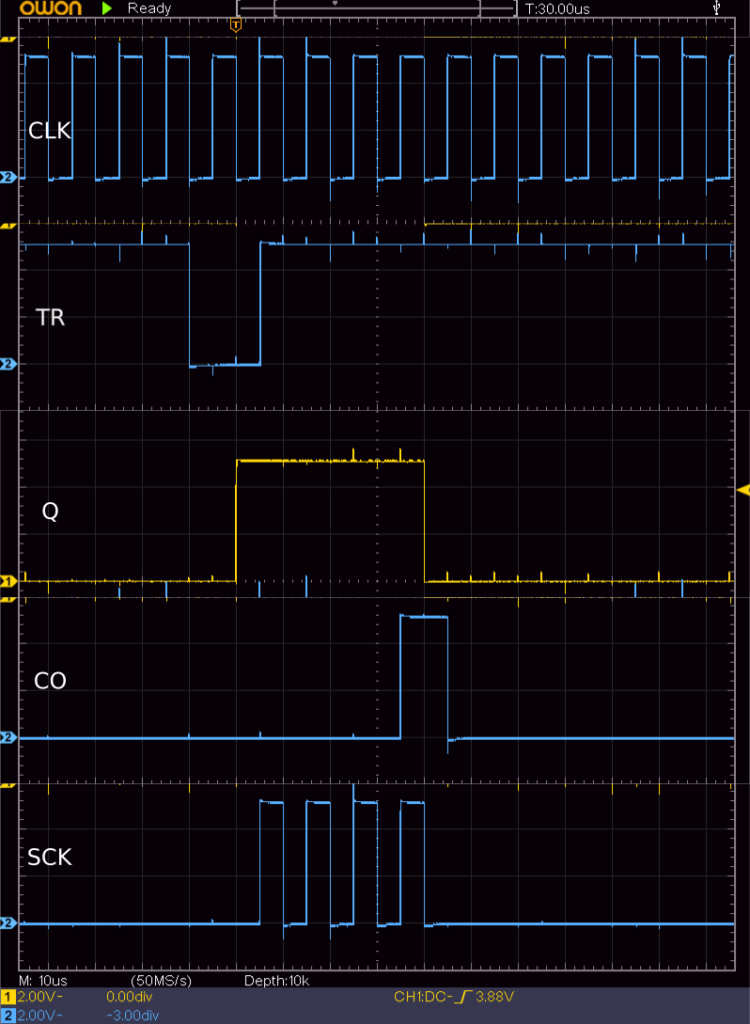

タイミングダイヤグラム

パルストレイン発生回路の基本的な考え方は、トリガ入力を受けてクロックパルスのカウントを開始し、設定したカウント数になったらカウンタを停止する、という方法です。

いつものように部品箱を覗き込み、部品を選定。カウンタには 4ビット同期カウンタ 74HC161 を利用し、JKフリップフロップ CD4027 でカウント動作の起動停止を行なうことにしました。基本的に同期回路とし、強制的にカウンタをリセットするような動作は避けたいと思います。

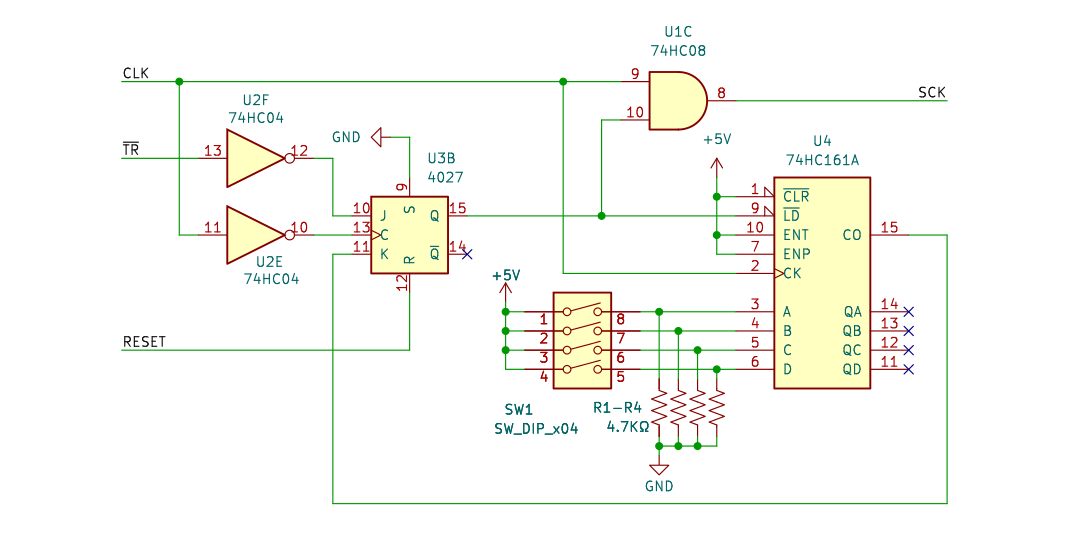

図1 がタイミングダイヤグラムです。

トリガパルス TR で JKフリップフロップをセットし、カウンタの入力データロード LD を HIGH にします。これによりカウントが開始されます。

カウンタが 0xF になるとキャリーオーバー CO が出力され、JKフリップフロップをリセット、LD を LOW にしてカウンタを停止します。同時に、初期値データをロードします。

TR が入力されると、以上の動作を繰り返します。

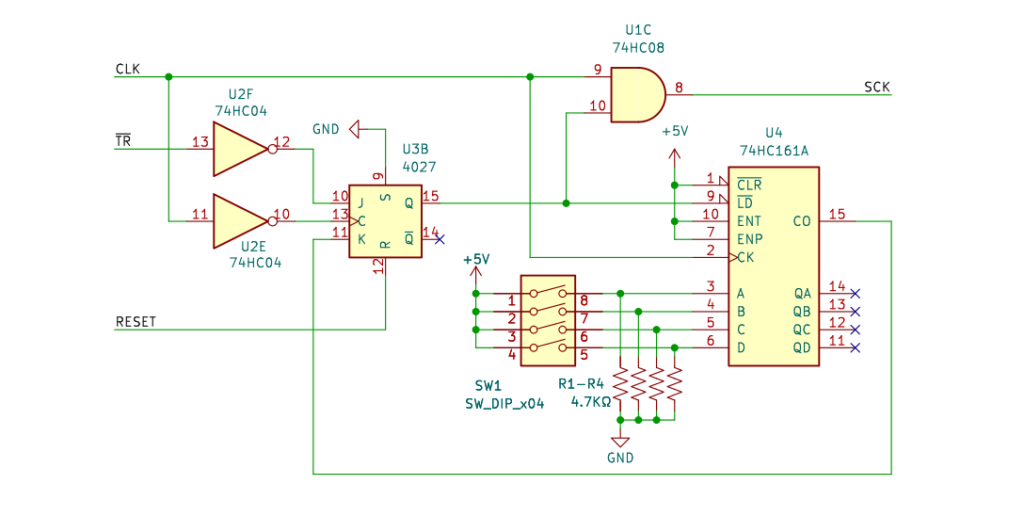

回路図

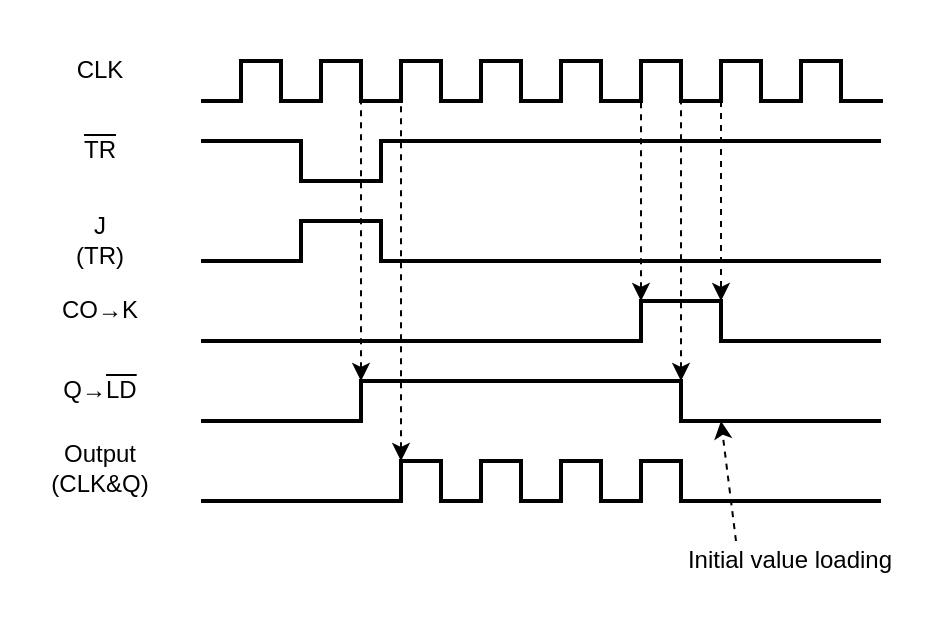

タイミングダイヤグラムを基に、パルストレイン発生回路と実験のための周辺回路をつくりました。

パルストレイン発生回路

トリガパルス TR は JKフリップフロップの入力 J をセットするために NOT で反転させています。また、クロック CLK も NOT で反転し、立ち下がりエッジで JKフリップフロップを動作させることで、カウンタより先行させています。

JKフリップフロップの出力 Q を カウンタの入力データロード LD に入力し、カウンタを制御します。74HC161 は LD を LOW にすると内部回路でカウンタイネーブル ENP を disable にしますので、カウント動作が停止します。そのため ENP、ENT を制御する必要はありません。

キャリーオーバー CO は JKフリップフロップの入力 K に接続し、JKフリップフロップをリセットします。

Q を AND ゲートに入れることで CLK の出力を制御し、クロックトレイン SCK を出力します。

入力データ ABCD につながれた Dipスイッチにより初期値を設定しています。カウンタは [初期値+1] から [0xF] までカウントし、CO を出力します。

たとえば Dipスイッチを 0xB としておくと、0xC、0xD、0xE、0xF と 4カウントしますから、4つのパルスが出力されます。0x7 ならば、0x8 ~ 0xF まで 8パルスを出力します。同様に 0x0 のときは 15パルス、0xF にすれば 16パルスを出力します。

実験用の周辺回路

パルストレイン発生回路を実際に動かして実験するために、周辺の回路をつくりましょう。

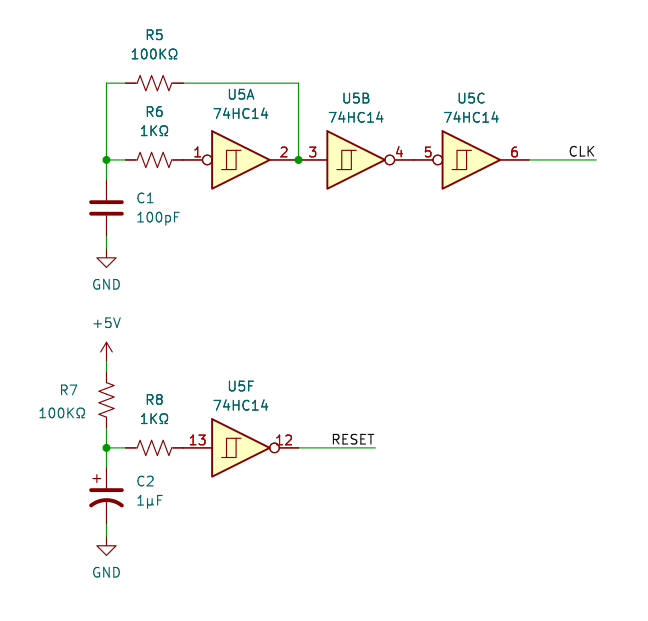

図3 上はクロック発振回路、毎度おなじみのシュミットトリガインバータを利用した矩形波発振回路です。

発振周波数は 100KHz です。100KHzにしたことにとくに理由はなくて、まぁ、気分です。

図3 下は、JKフリップフロップの初期化回路です。こちらも毎度おなじみのタイマ回路。

電源オン時に 100ms の正パルスを出力します。これを JKフリップフロップの RESET に入力することで初期化します。

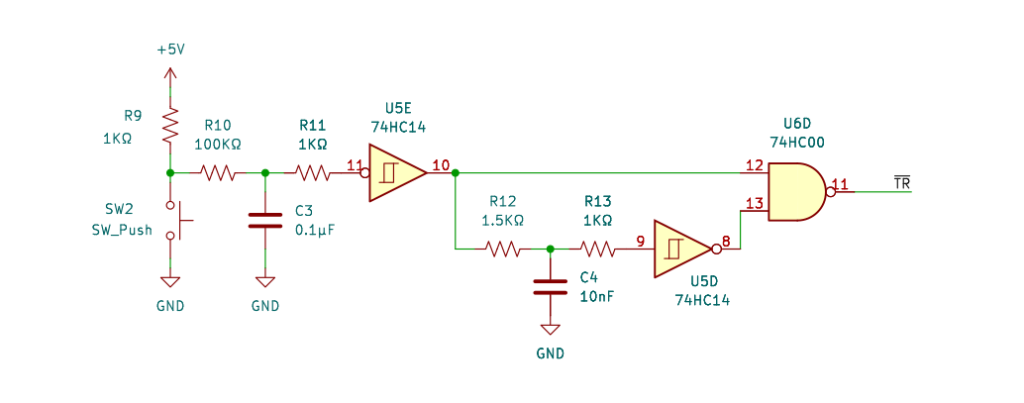

図4 は、パルストレイン発生回路を起動するトリガパルスの発生回路です。

トリガ信号を LOW で継続すると、繰返しパルストレインが出力されてしまいます。そこで、トリガをワンショットとすることで、1回だけ回路を動かすようにしました。

押しボタンスイッチにつながるローパスフィルタ R10、C3 とシュミットトリガインバータ U5E は、スイッチのチャタリング防止回路です。遅延時間は 12msです。次のローパスフィルタ R12、C4 とシュミットトリガインバータ U5D、ANDゲート U6D の組み合わせは、ワンショットパルス発生回路です。ワンショットパルスは負パルスで、幅 15μs。クロック周期の 1.5倍です。

電源は +5Vです。回路は描いていませんが、9Vの ACアダプタ電源を三端子レギュレータ 7805 で 5Vにしています。これはなんでもいいです。5Vの ACアダプタでも USBでも、お好みでどうぞ。

出力波形

図5は、実際の各部の波形をタイミングダイヤグラムに合わせて合成したものです。

一番上がクロック CLK です。周期は 10μsです。

2つ目がトリガパルス TR 、負のパルスで幅 15μsです。

トリガパルス回路は非同期な回路なのですが、不思議なことに CLK の立ち下がりエッジに同期しています。どうやら、押しボタンスイッチまわりのゆっくり動く信号が、クロックのノイズに影響されているみたいです。

3つ目 (黄) が JKフリップフロップの出力 Q で、カウンタの動作を制御する LD になります。これが HIGH のあいだ、パルストレインが出力されます。

下から 2つ目。カウンタからのキャリーオーバー CO で、JKフリップフロップをリセットします。

最後が出力されたパルストレイン SCK。4クロックのパルス列になっています。

ということで、当初計画したタイミングダイヤグラムと同じ結果になりました。

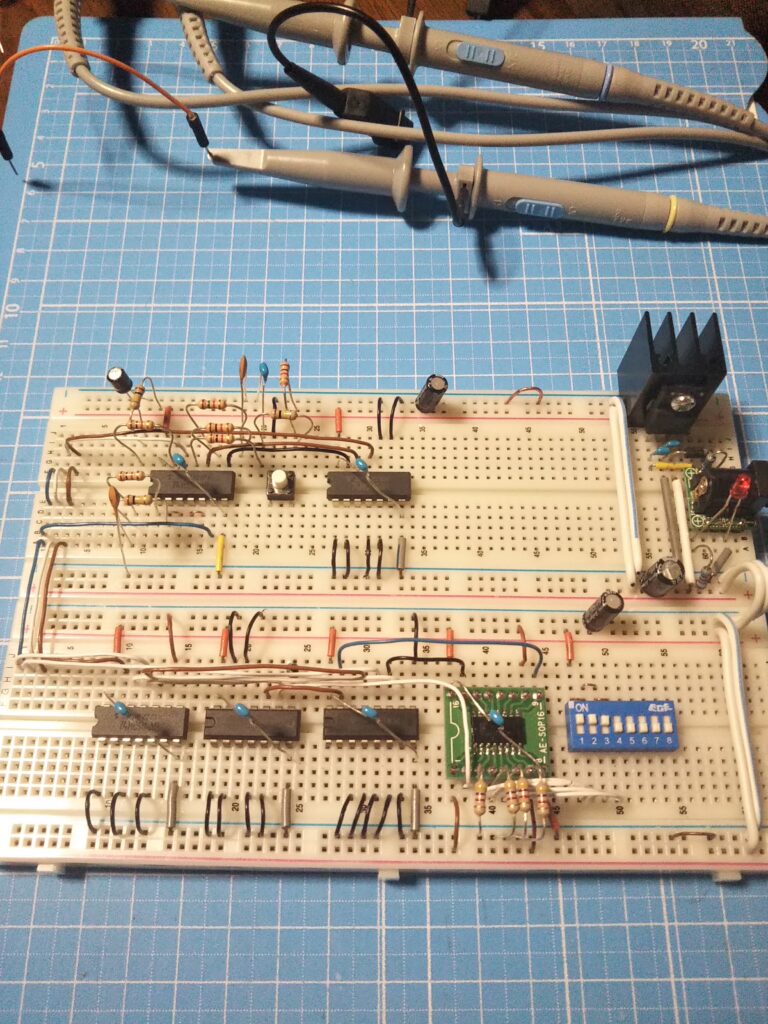

ブレッドボード

実験したブレッドボードのようすです。

左上部が、クロック発振回路、初期化回路、ワンショットトリガパルス発生回路の 74HC14 と 74HC00 です。あいだに押しボタンスイッチがあります。

右上部はまいどの +5V電源部です。

下のブレッドボードがパルストレイン発生回路。

左から、74HC04、74HC08、CD4027、変換基板に載っているのが 74HC161 です。いちばん右は Dipスイッチ。回路図では 4ビットですが、実験では 8ビットを使っています。

ま、こんな感じでやりました、ってことで。

後記

今回は、一定の数のパルス列を出力するパルストレイン発生回路をつくってみました。

このパルストレイン発生回路は、SPI コントローラのシリアルクロックに使えるんじゃないですか。こうしていろいろにパルスを制御できるようになったら、きっとつくれる回路も増えきますよね。またいろいろ考えてみようと思います。