JKフリップフロップを使ったカウンタ回路をつくってみました。

2進~10進同期カウンタは、前回の記事を参照ください。

Dフリップフロップを使ったカウンタ回路は下記を参照ください。

11進~16進同期カウンタ

JKフリップフロップを使用した 11進~16進同期バイナリアップカウンタの回路例です。

フリップフロップとかカウンタとか真理値表とかカルノー図とか、基本的なことは教科書みるか、グーグル先生に尋ねてください。なお、シミュレーションは、verilogHDL によって論理式について行なっており、回路図と連動していません。回路はじっさいに製作しておらず、動作を確認していません。

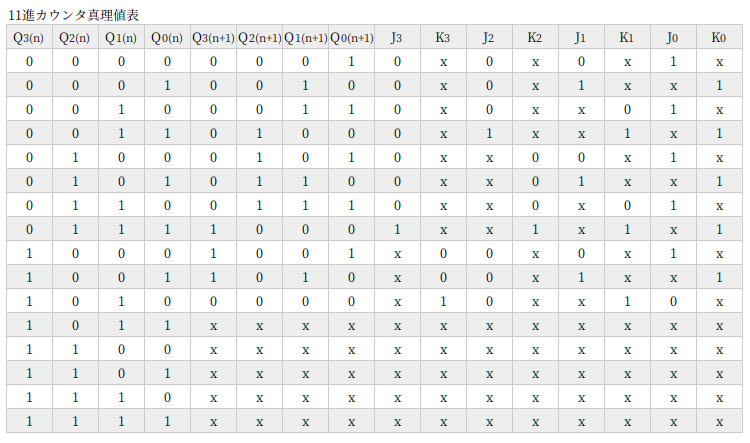

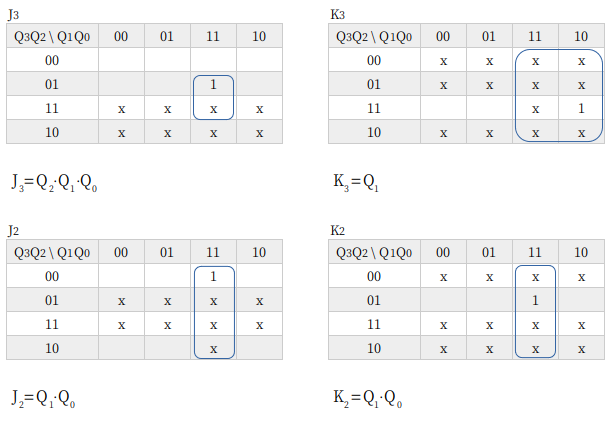

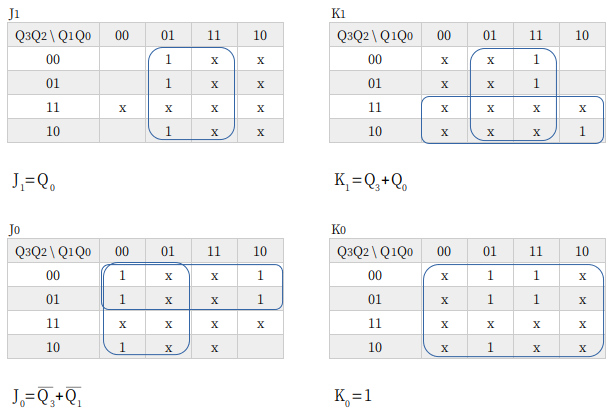

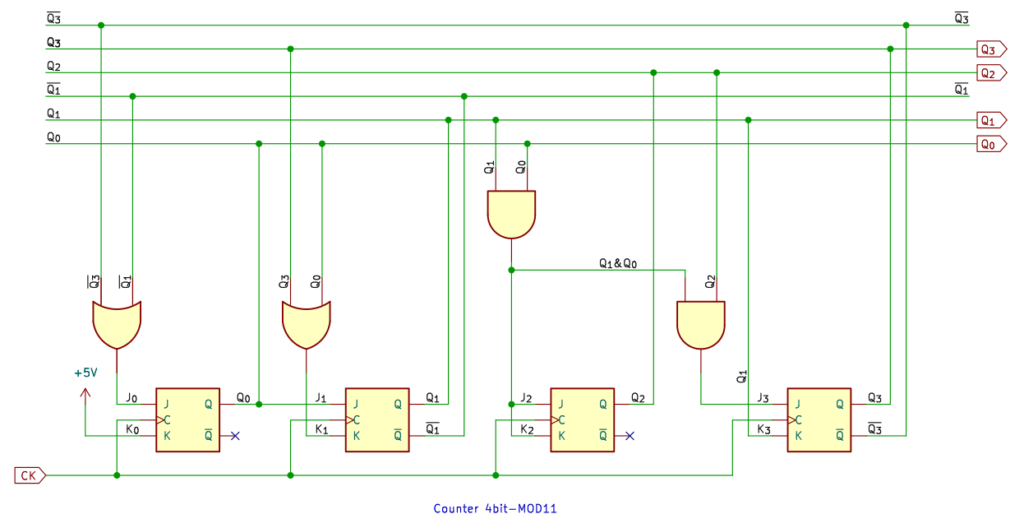

11進カウンタ

11進カウンタ。考え方はこれまでと同様で、変わったことはないです。

7進カウンタでもありましたけど、ド・モルガン変換して反転出力を使わないとかもできます。どのゲートIC を使うかによって考えていけばよいです。

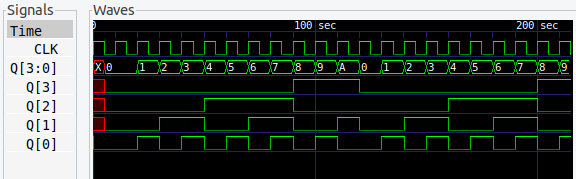

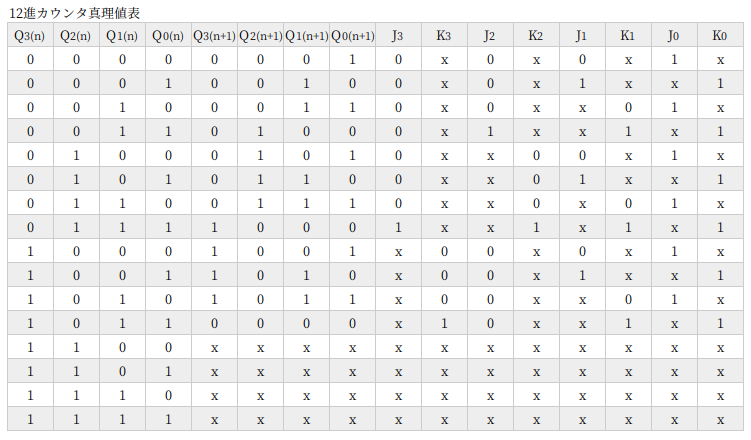

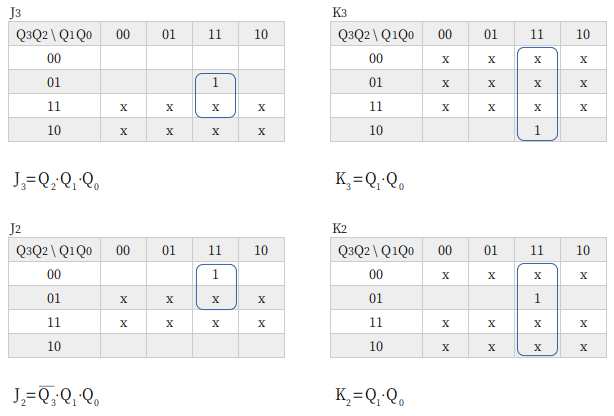

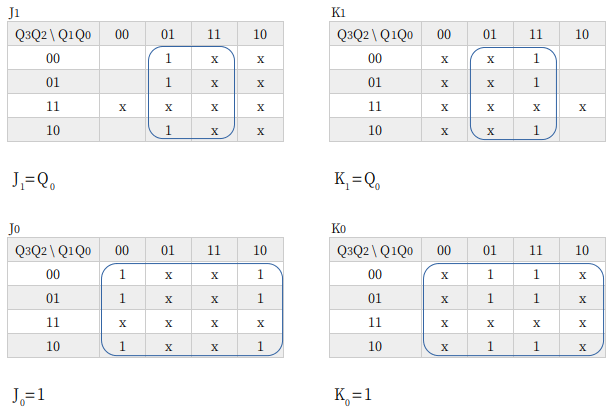

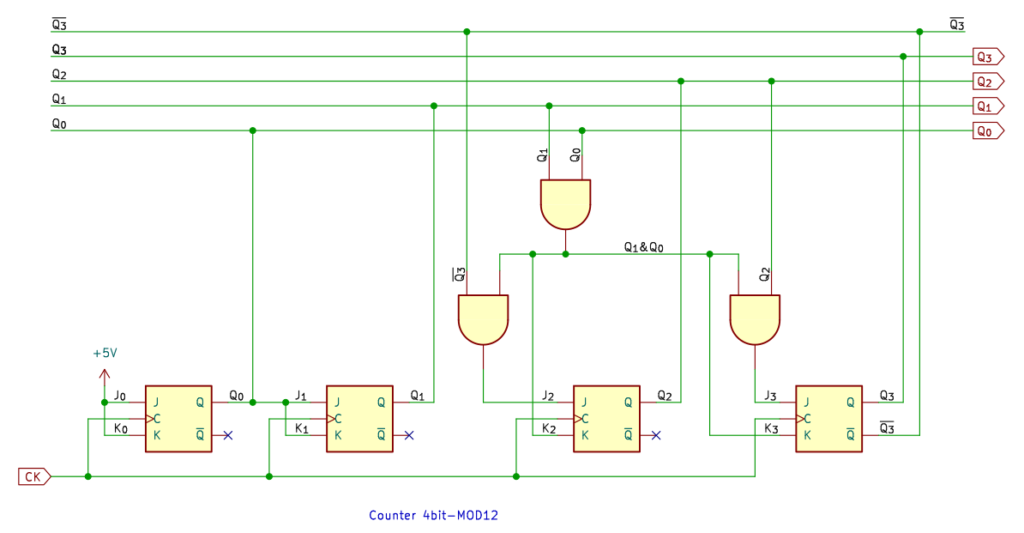

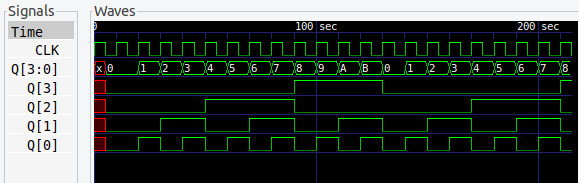

12進カウンタ

12進カウンタ。このあたりになってくると、Dフリップフロップをつかう場合よりずっと簡単な回路になるんで、やっぱり JKフリップフロップ使いたくなります。

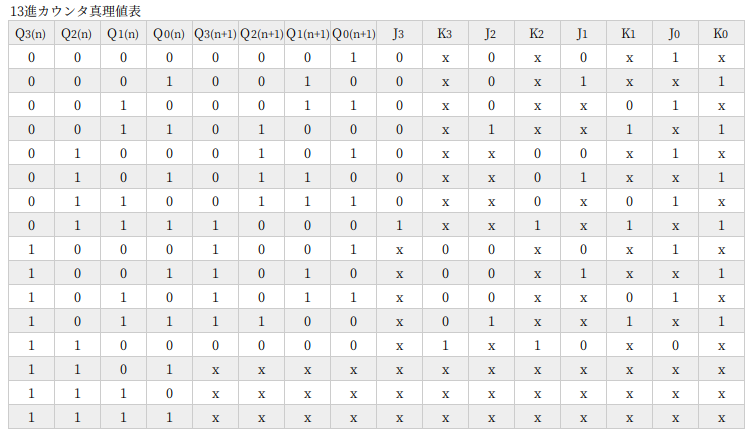

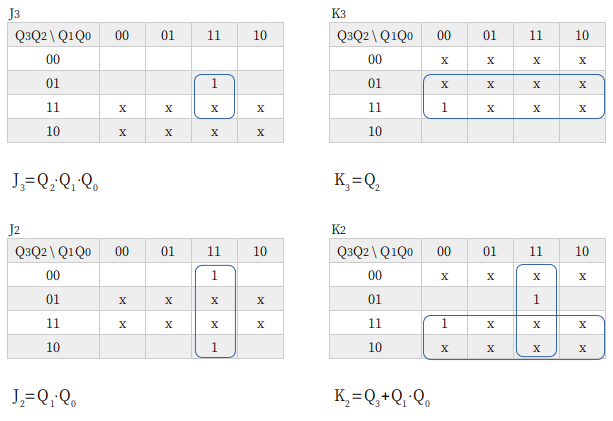

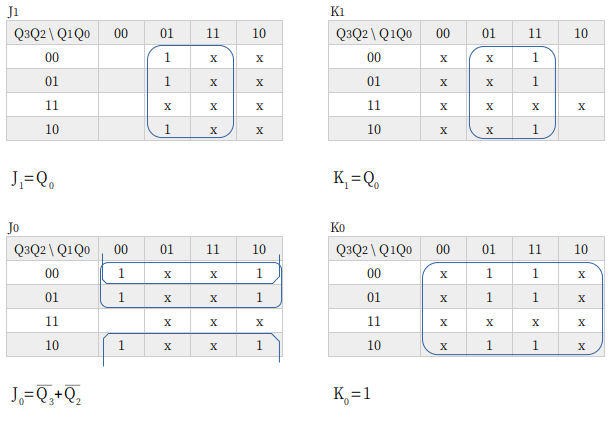

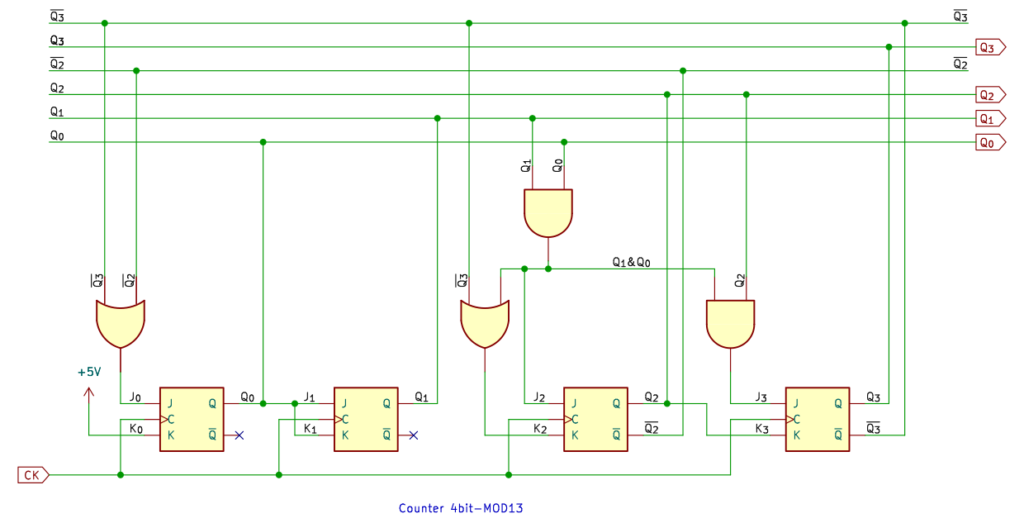

13進カウンタ

13進カウンタ。11進とか12進とかと似ているような違うような、そんな感じです。

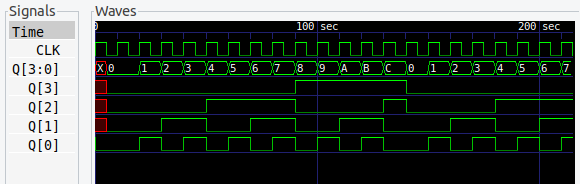

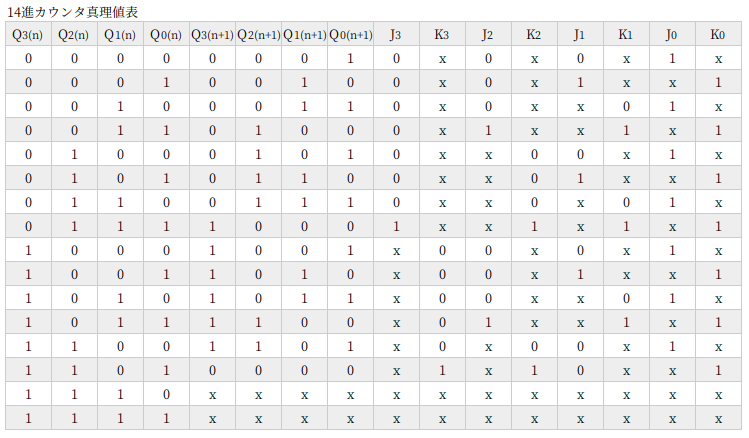

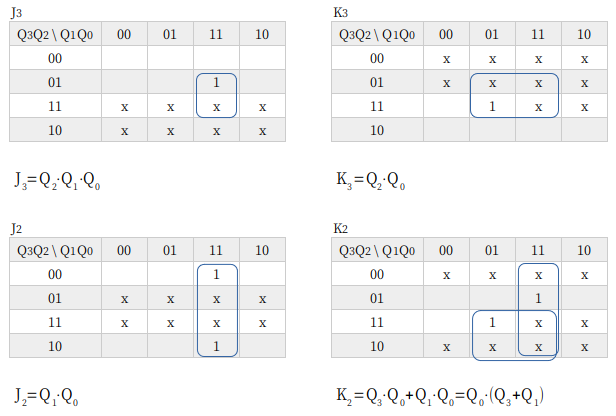

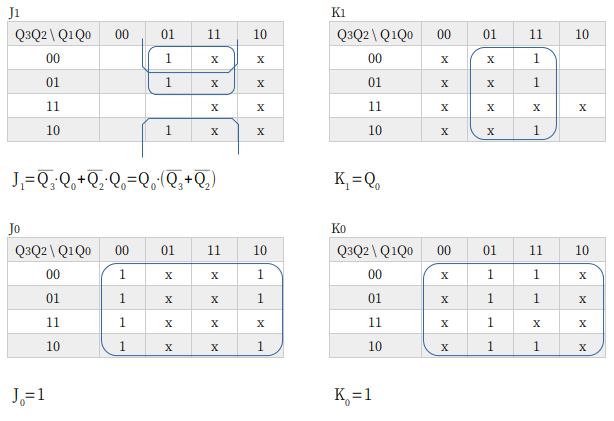

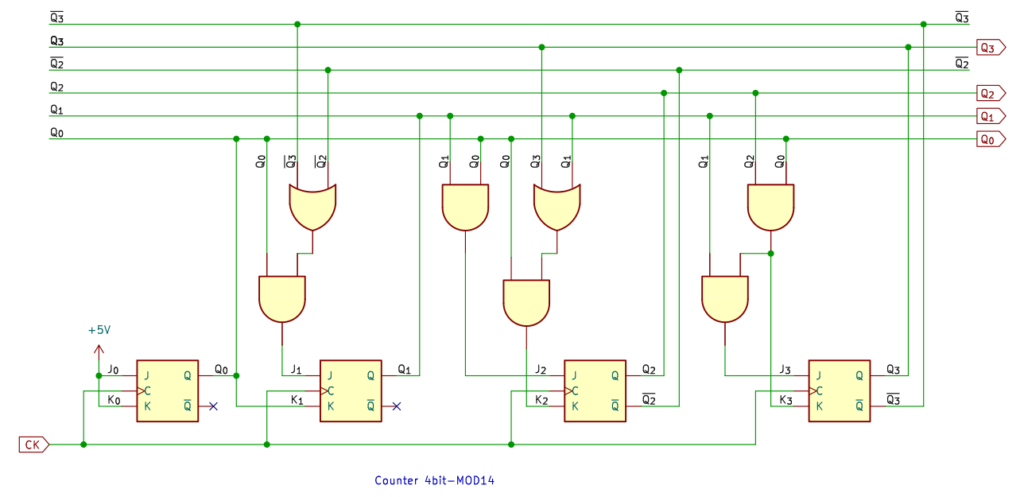

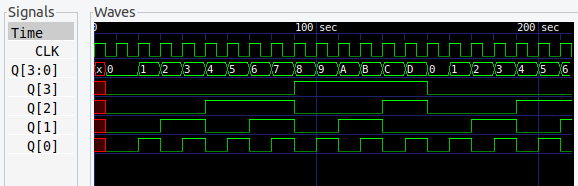

14進カウンタ

ちょっと複雑そうにもみえますが、Dフリップフロップの 14進カウンタと比べりゃ簡単なものです。

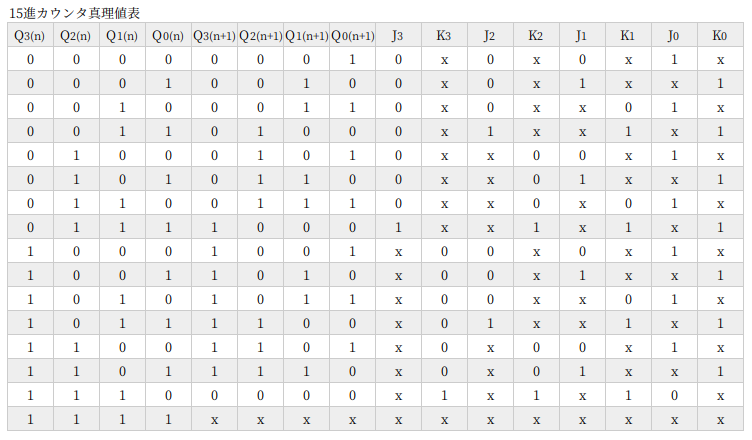

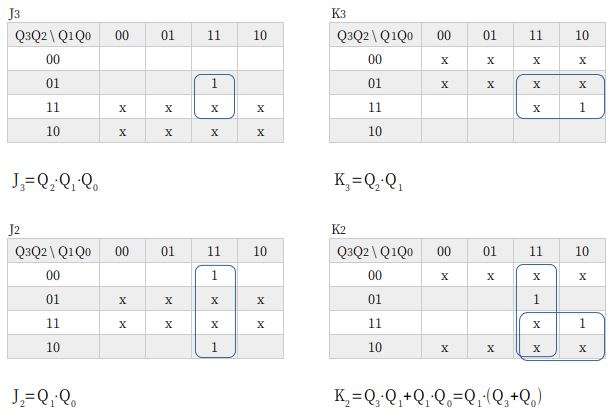

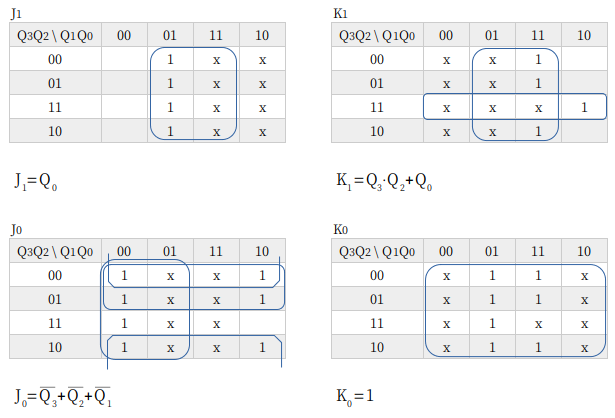

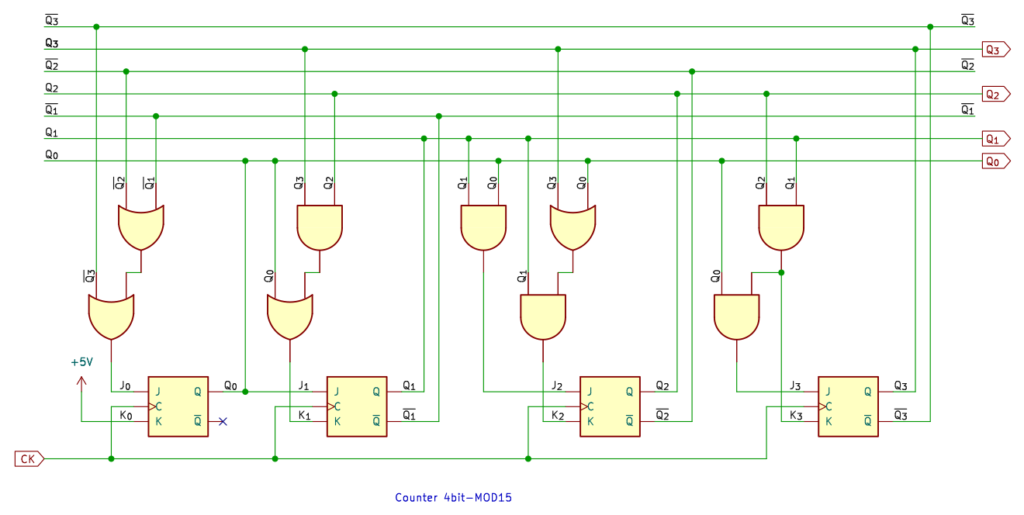

15進カウンタ

15進カウンタは、JKフリップフロップ使用のなかでいちばん複雑かもしれません。

J0 のゲート回路は 2入力OR 使ってますが、もちろん 3入力OR でもいいです。74HC4075 ですね。

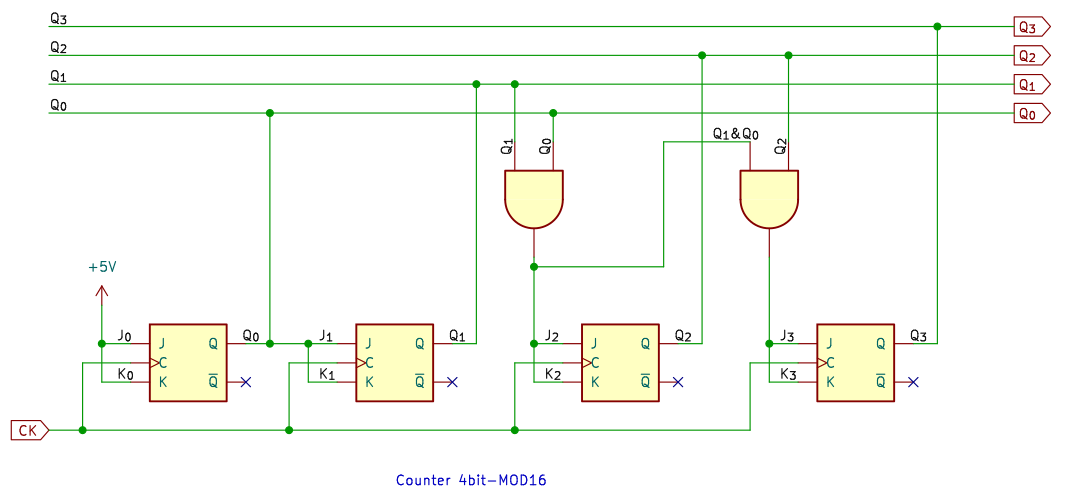

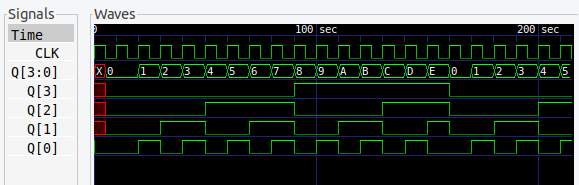

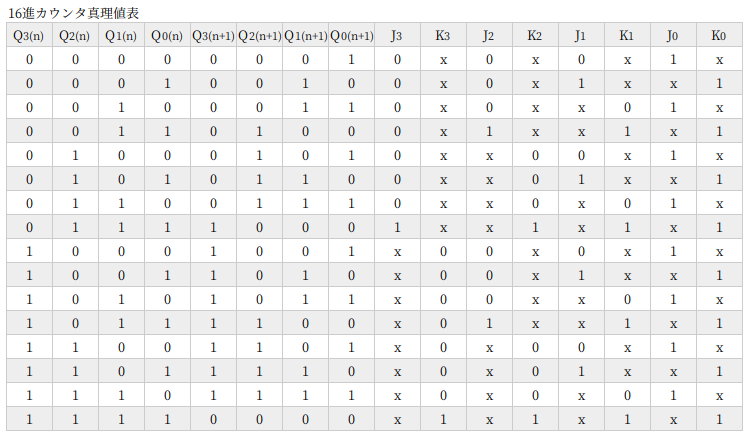

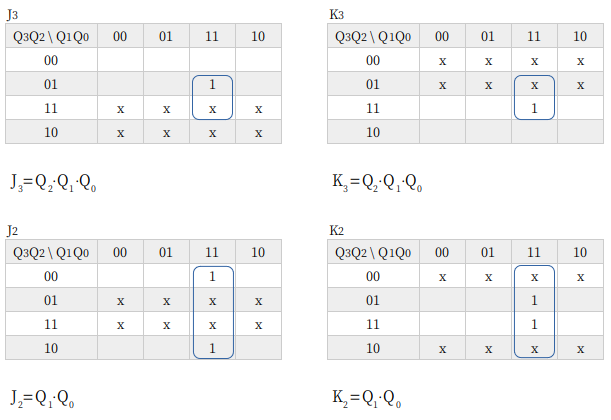

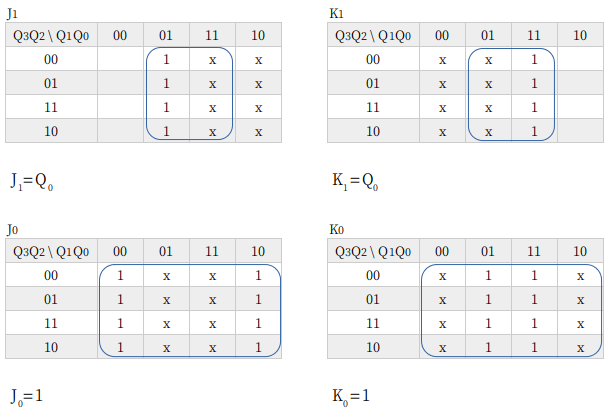

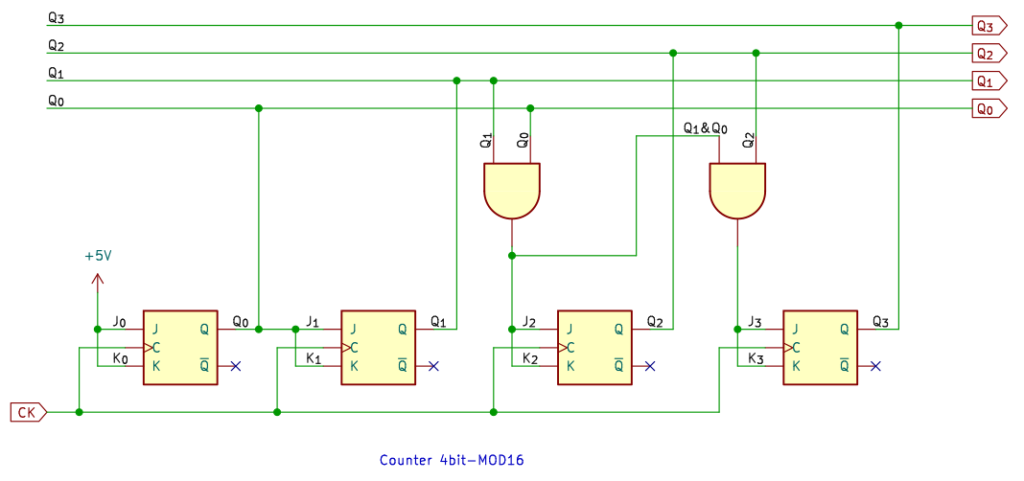

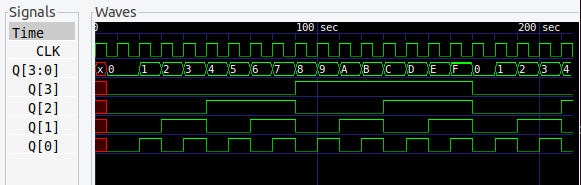

16進カウンタ

最後に 16進カウンタ、(2n)進の基本的な回路です。

後記

前回の 2進~10進カウンタに続いて、JKフリップフロップを使った 11進~16進カウンタ回路をつくってきました。

特に解説することもないので、ほとんど真理値表と回路図だけになっちゃいました。JKフリップフロップの動作が理解できれば、真理値表 (励起表) をつくることはむずかしくないと思います。それができれば、あとはフリップフロップだろうが組み合わせ回路だろうがやることは同じです。

最後に、論理式の簡単化をしてくれる便利なサイトを紹介しておきます。

今回やったような 4ビットカウンタまでならチャチャッとできちゃいますが、5ビット、6ビットとなるとかなり面倒なので、こうしたツールを使うと楽になります。

世の中にはもっと便利なツールもあるんだろうなぁと思うんで、ご存知だったら教えてくださいませ。