4bit 同期バイナリカウンタ 74HC161A のカウンタ動作が確認できたので、今回は、イネーブル付きの 10進カウンタをつくってみようと思います。

イネーブル付き 10進カウンタを構成する

74HC161A で10進カウンタを構成する考え方は、これまで学んできたこと (過去記事) と同じです。むしろフリップフロップで構成するより簡単。出力が 9 になったら 0 をロードしてやればいい。ただし、これまで同様に、カウンタをリセットするなどという荒業はしません。74HC161A にはプリセットデータを同期ロードする機能 (LD) があるのですから、それを利用します。

組み合わせ回路を構成する

出力 Q が 0x9 になったら、プリセットデータ PRE=0x0 をロード LD する。それだけなので、論理式は、

LD = QD⋅QA

10進カウンタの回路を VerilogHDL で記述します。前回記述した 74HC161A を下位モジュール接続し、ENP は HIGH、プリセットデータ PRE は 0x0 としました。

- module COUNTER_MOD10 (

- input wire CK, CLR, ENT,

- output wire [3:0] Q

- );

- assign LD = ~(Q[3] & Q[0]);

- TC74HC161A U1(CK, CLR, LD, ENT, 1'b1, 4'h0, Q, CO);

- endmodule

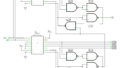

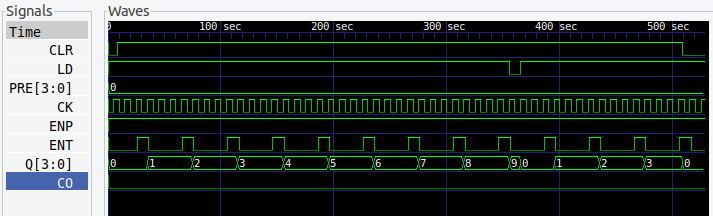

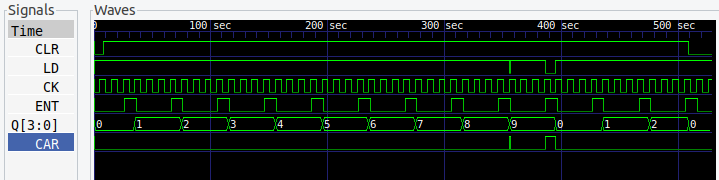

下位カウンタ (4進) から ENT が送られてきているとして、シミュレーションしてみたのが図1 です。

出力は、たしかに 9 の次が 0 になっていますが、うーん、なんだか変ですねぇ。LD が ENT より優先なので、ENT に関係なく 0x0 をロードしてしまっています。これはうまくありません。

また、出力が 0xf にならないのでキャリー信号 CO が出力されません。

そこで、ロードの条件に ENT を加えてみます。同時に、組み合わせ回路からキャリー信号 CAR を出力するようにしました。

CAR = ENT⋅QD⋅QA LD = CAR

- module COUNTER_MOD10 (

- input wire CK, CLR, ENT,

- output wire [3:0] Q,

- output wire CAR

- );

- assign CAR = ENT & Q[3] & Q[0];

- assign LD = ~CAR;

- TC74HC161A U1(CK, CLR, LD, ENT, 1'b1, 4'h0, Q, CO);

- endmodule

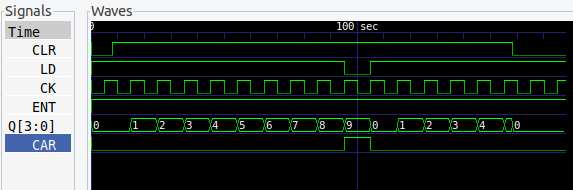

これをシミュレーションしたのが図2 です。

ENT で制御された 10進カウンタになりました。キャリー信号もでています。

出力が 0x9 に遷移したときに、/LD と CAR に細いパルス (ハザード) がでています。これは、CK が入って Q が 0x9 に遷移してから ENT が LOW になるまでの遅延によるものです。シミュレーションでは ENT の遅延時間を 1sec としているために目立ってますが、実際の回路では 10ns 程度のノイズでした。動作には影響がないと思うので、特に対策はしていません。

最下位のカウンタとして利用する場合の、ENT を HIGH にしたときのシミュレーションもしておきましょう。(図3)

普通に 10進カウンタとなることが確認できました。

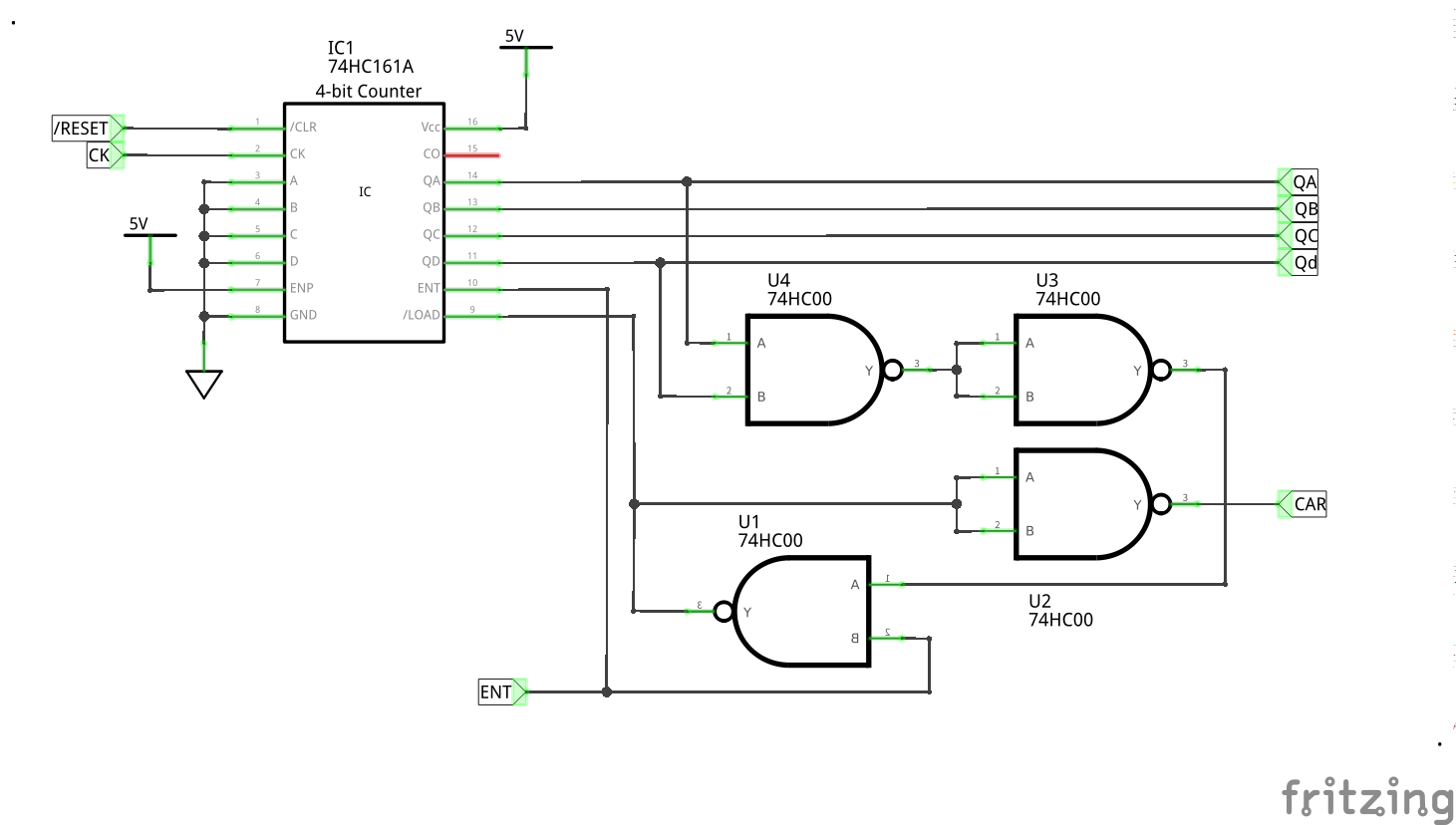

回路図

ということで、つくった回路が図4 です。そうむずかしくない回路なので、先に回路をつくっちゃって、それをシミュレーションしてみた、んですケド (^_^;)

74HC00 (NAND) 1個でつくるために論理式を変形していますが、解説するほどのことではないですね。

/RESET は HIGH にしてください。電源オン時に遅延して立ち上げるのがおすすめです。

ちなみに、ゲートに入れる出力を n に変更すれば n進カウンタにできます。

たとえば QA と QC ならば 6進カウンタになります。それを 10進カウンタとつなげれば 60進カウンタ。デジタル時計の秒・分カウンタに使えますね。

後記

10進カウンタなら BCD出力の 74HC160 や 74HC162 を使えばいいんじゃね?

そのとおりだと思います、手に入るのなら。でも、74HC160 で 16進カウンタはできないので、いろいろ試してみたい俺は、秋月電子通商にあった 74HC161A を買いました。

とゆーことで。次は、60進カウンタにしてみましょうか。

74HC161A / 4bit 同期バイナリカウンタIC を使ってみる

74HC161A / イネーブル付き 10進カウンタをつくる

74HC161A / 同期 60進カウンタをつくる

74HC161A / 時表示用 12進カウンタをつくる

74HC161A / 時計用の 2Hzクロックをつくる

74HC161A版 デジタル時計 / 時刻合わせ回路

74HC161A版 デジタル時計 / 7セグLED表示回路(仮)

74HC161A版 デジタル時計 / カウンタ部を基板に組む

74HC161A版 デジタル時計 / バイナリ表示器をつくる

74HC161A版 デジタル時計 / 7セグメントLED 表示器をつくる

74HC161A版 デジタル時計 / リングLED 表示器をつくる