74HC161A は 4bit 同期カウンタ IC、バイナリ出力のアップカウント動作を行ないます。同期プリセット付、非同期クリアタイプで、同期型カスケード接続のためのイネーブル入力とキャリー出力を備えています。

今回は、この 74HC161A のカウンタ動作を試してみました。

ちなみに、購入したのは SOP16 タイプです。DIP16 がほしかったんですけど、秋月電子通商にありませんでした。他社にはあったんですけど、変換基板とヘッダピンを含めても、こっちのほうが安かったとゆ〜。

老眼にはハンダ付けがつらい (;´Д`)

74HC161Aの動作概要

各入出力の概要をみていきます。(参照データシート:TC74HC161AF)

バイナリ出力 QA QB QC QD

カウンタの出力、4bit のバイナリデータで、QA が LSB、QD が MSB になっています。

キャリー出力 CO

キャリー (桁上がり) 信号 (Carry Over) で、カウンタ出力が 0xF のときに HIGH になります。

真理値表に記載されていないので詳細な動きがわかりにくいのですが、真理値表の脚注に「Carry=ENT⋅QA⋅QB⋅QC⋅QD」と記載されていることと、システム図から動作が推測できます。

詳細は後述します。

クロック入力 CK

クロック CK は、立ち上がりエッジで動作します。CLR は非同期ですが、他はすべて CK に同期します。

クリア入力 CLR

負理論入力、つまり LOW のときに有効になる入力です。CLR を LOW にすると、カウンタはすべて 0 にリセットされます。クロック CK に無関係な非同期リセットで、すべての動作に優先します。

ロード入力 LD

LD は Load の略。LD が LOW になると、プリセット入力 A、B、C、D がそれぞれ出力 QA、QB、QC、QD にセットされます。プリセット動作はクロック CK の立ち上がりエッジに同期します。

優先順位は CLR の次で、ENP、ENT に優先します。また、LD が LOW の間は、カウンタは停止します。

入力 ENT ENP

ENP は Enable Preset、ENT は Enable Trigger の略、らしい。LOW にするとカウントが停止します。カウントさせるには、両方を HIGH にする必要があります。

データシートの標準応用例によると、ENP はすべてのカウンタのイネーブル制御に利用する。ENT は下位カウンタの桁上がり信号 CO を入力し、カウントイネーブルに使用する。ということになっています。

ENP と ENT は、どこが違うのか。

ENP は、単純にカウンタ動作を停止します。

ENT も、同様にカウンタ動作を停止しますが、CO が出力されている (HIGH) ときに ENT を LOW にすると、CO も LOW に落ちます。ENT を HIGH にもどすと、CO も HIGH になり、カウンタ動作を再開します。

ENP は、CO に影響しません。

優先順位は LD の下なので、ENP、ENT が LOW でカウンタが停止していても、LD によるプリセット動作は実行されます。

VerilogHDL によるシミュレーション

じっさいに回路をつくって動作を確認してみているのですが、その結果も踏まえて、VerilogHDL で 74HC161A のモジュールをつくりました。それをシミュレーションした結果です。

- module TC74HC161A (

- input wire CK, CLR, LD, ENT, ENP,

- input wire [3:0] PRE,

- output reg [3:0] Q,

- output wire CO

- );

- always @(posedge CK, negedge CLR) begin

- if(1'b0 == CLR) begin

- Q <= 4'h0;

- end

- else if(1'b0 == LD) begin

- Q <= PRE;

- end

- else if(1'b0 == ENT || 1'b0 == ENP) begin

- end

- else begin

- Q <= Q + 4'h1;

- end

- end

- assign CO = (1'b1 == ENT && 4'hf == Q);

- endmodule

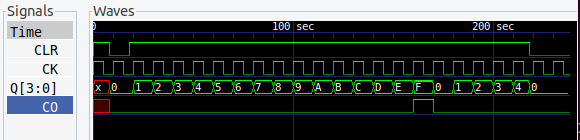

まず、ごく普通に、16進カウンタとして動作させてみました。(図2)

LD、ENP、ENT はすべて HIGH にしてあります。

CLR を LOW にすると、クロックには同期せずにカウンタはリセットされます。CLR を HIGH にすると 0x0~0xF をカウントし、0xF で CO を出力して 0 にもどります。

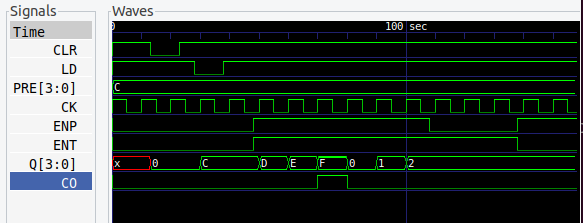

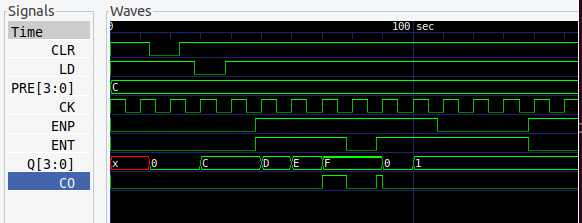

つぎに、データシートに載っているタイミング図と同じような状態をつくってみました。(図3)

PRE は、プリセット入力 A、B、C、D を 4bit 表記したものです。A が LSB、D がMSB で、A、B、C、D に入力した値は、それぞれ QA、QB、QC、QD にプリセットされます。

起動時に不定になっていた出力が CLR によりリセットされ、LD で PRE の値 0xC をプリセット。ENP、ENT が HIGH になるとカウントが始まり、0xF で CO を出力、0 にもどってカウントを継続する。ENP が LOW になるとカウントを停止し、ENT と 共に HIGH にならなければカウントは再開されない。

そんなようすが再現できました。

最後に、ENT と CO の動きの関連を確認しておきましょう。(図4)

CO が出力されているときに ENT を LOW にすると、カウントが停止すると同時に CO が LOW になる。ENT を HIGH にもどすと、CO はふたたび出力され、カウントが再開される。

図には表れていませんが、ENP でカウントを停止したときは、CO は変化しません。

後記

今回は、74HC161A の基本的なカウント動作を試してみました。

4bit 同期カウンタについては、以前にフリップフロップを使って試しています (過去記事) ので、その動作は理解できていると思います。この IC は、システム図をみると複雑そうですが、Dフリップフロップが 4個入っているだけ。組み合わせ回路はプリセットやキャリーなどのためのもので、カウンタとしての基本動作はかわりありません。

なので、こいつで 10進カウンタなどをつくることも可能なはず。次回はそのあたりを試してみようかと思います。

74HC161A / 4bit 同期バイナリカウンタIC を使ってみる

74HC161A / イネーブル付き 10進カウンタをつくる

74HC161A / 同期 60進カウンタをつくる

74HC161A / 時表示用 12進カウンタをつくる

74HC161A / 時計用の 2Hzクロックをつくる

74HC161A版 デジタル時計 / 時刻合わせ回路

74HC161A版 デジタル時計 / 7セグLED表示回路(仮)

74HC161A版 デジタル時計 / カウンタ部を基板に組む

74HC161A版 デジタル時計 / バイナリ表示器をつくる

74HC161A版 デジタル時計 / 7セグメントLED 表示器をつくる

74HC161A版 デジタル時計 / リングLED 表示器をつくる