4bit 同期バイナリカウンタ 74HC161A を使ってイネーブル付き 10進カウンタができましたので、今回は 60進カウンタをつくりましょう。これは、以前つくったデジタル時計の 60進カウンタ (過去記事) に置き換えることができます。

同期 60進カウンタを構成する

前回もちょこっと書きましたが、10進カウンタのゲート入力を 0x9 から 0x5 に変更すれば 6進カウンタになります。そいつを 10進カウンタとつなげば 60進カウンタになる。それだけです。

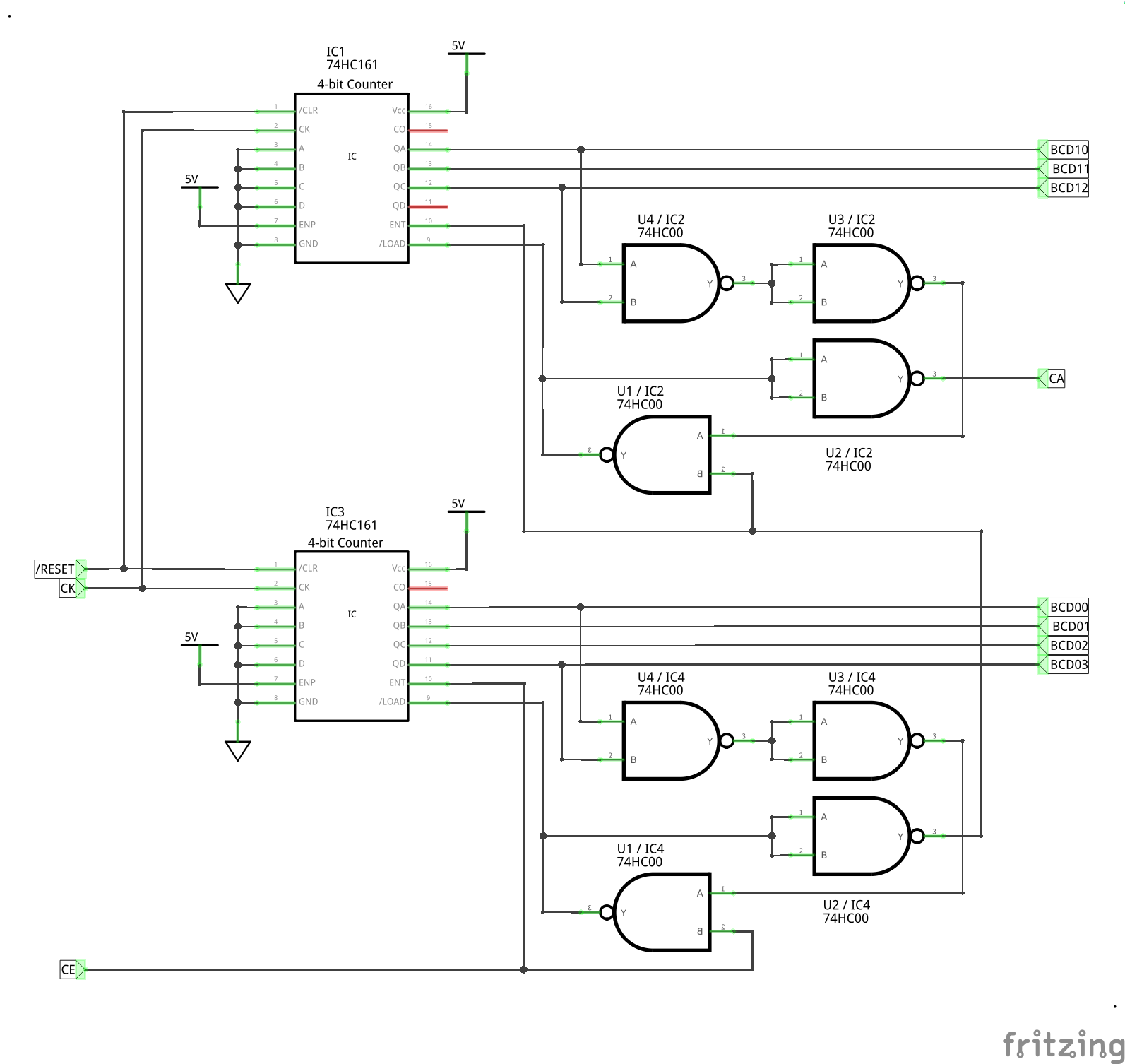

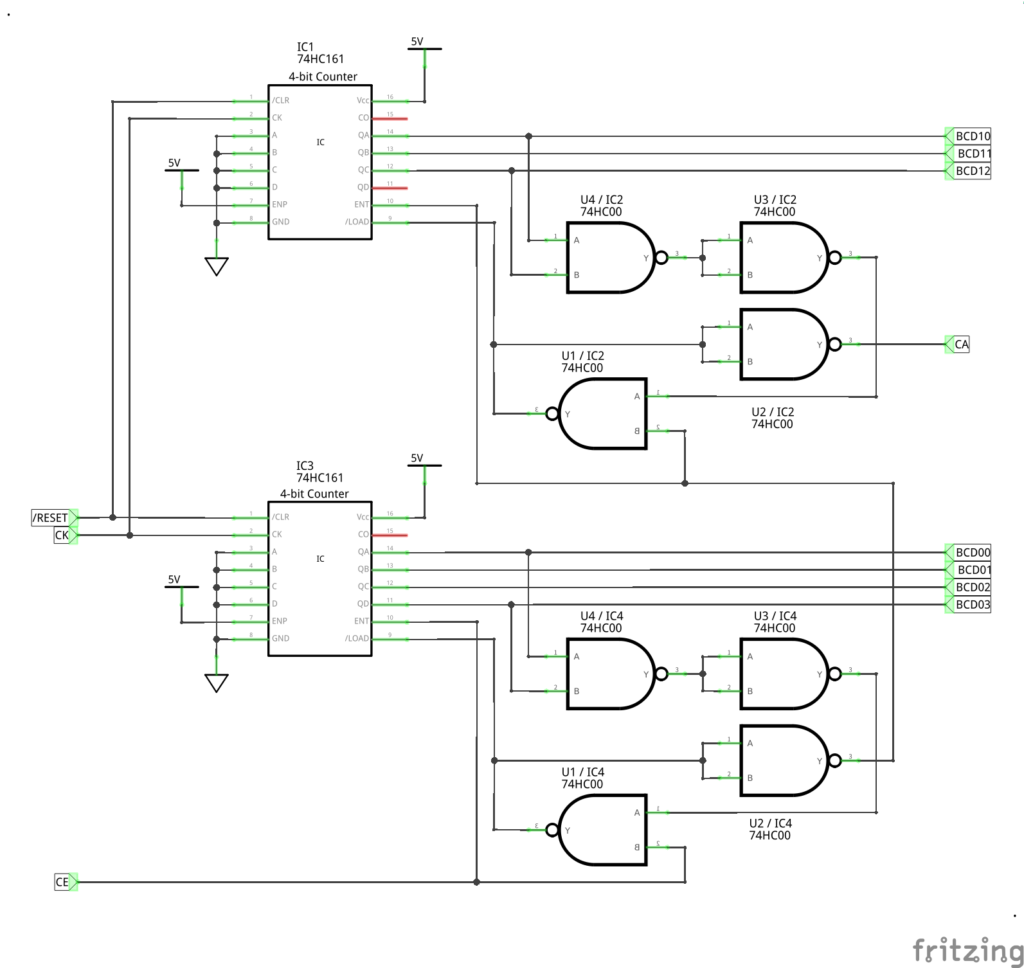

同期 60進カウンタ回路図

回路図です。(図1)

下部が 10進カウンタ。

デジタル時計の回路に合わせて、イネーブル入力は CE にしてあります。キャリーは、6進カウンタのイネーブルとしてわたします。

上部が 6進カウンタ。

組み合わせ回路に 0x5 を入力している以外は、10進カウンタと同じです。キャリー出力 CA は上位カウンタへの桁上がり信号で、59 で出力されます。

出力は、10進カウンタから 1の位の 0x0~0x9、6進カウンタから 10の位の 0x0~0x5 がでます。BCD なので、それぞれ 7セグメントLED デコーダなんぞにつなぐだけです。

動作シミュレーション

VerilogHDL で、60進カウンタの動作を確認しておきましょう。

前につくった 74HC161A を下位モジュールとし、6進カウンタと 10進カウンタを構成してつなげています。信号名とかが変わっていますが、基本的に 10進カウンタのときと同じです。

- module COUNTER_MOD60 (

- input wire CK, RESET, CE,

- output wire [3:0] Q1,

- output wire [3:0] Q0,

- output wire CA

- );

- wire LD0, LD1, CA0;

- assign CA0 = CE & Q0[3] & Q0[0];

- assign LD0 = ~CA0;

- assign CA = CA0 & Q1[2] & Q1[0];

- assign LD1 = ~CA;

- TC74HC161A U0(CK, RESET, LD0, CE, 1'b1, 4'h0, Q0, CO);

- TC74HC161A U1(CK, RESET, LD1, CA0, 1'b1, 4'h0, Q1, C0);

- endmodule

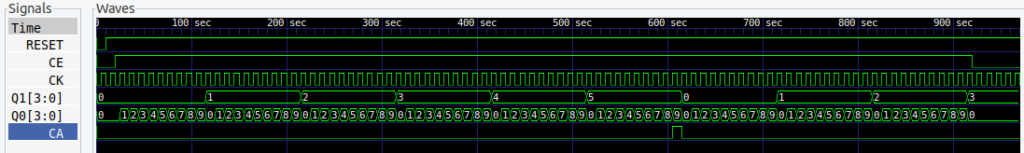

シミュレーションの結果は、図2 のとおりです。

イネーブル入力 CE が HIGH になるとカウントを開始し、出力が 59 のときにキャリー出力 CA が HIGH になっています。問題ないですね。

後記

さてと、60進カウンタができたってことは、次は 12進カウンタですなぁ (^_^;)

デジタル時計を、またつくっちゃいましょうか。

74HC161A / 4bit 同期バイナリカウンタIC を使ってみる

74HC161A / イネーブル付き 10進カウンタをつくる

74HC161A / 同期 60進カウンタをつくる

74HC161A / 時表示用 12進カウンタをつくる

74HC161A / 時計用の 2Hzクロックをつくる

74HC161A版 デジタル時計 / 時刻合わせ回路

74HC161A版 デジタル時計 / 7セグLED表示回路(仮)

74HC161A版 デジタル時計 / カウンタ部を基板に組む

74HC161A版 デジタル時計 / バイナリ表示器をつくる

74HC161A版 デジタル時計 / 7セグメントLED 表示器をつくる

74HC161A版 デジタル時計 / リングLED 表示器をつくる