4bit 同期バイナリカウンタ 74HC161A を使って 60進カウンタができました。これで、秒と分のカウントができますから、やっぱり次は、時をカウントする 12進カウンタをつくらないといけない、のです。

フリップフロップを使ったカウンタについては、こちらもあわせてご覧ください。

時表示用 12進カウンタ回路

時表示用のカウンタは、単純に 12 数えるだけではダメです。時刻は 12時から始まって、12時に終わるのですから。しかも、午前と午後がある。考えるほどに、だんだん、頭が、痛くなる (;´Д`)

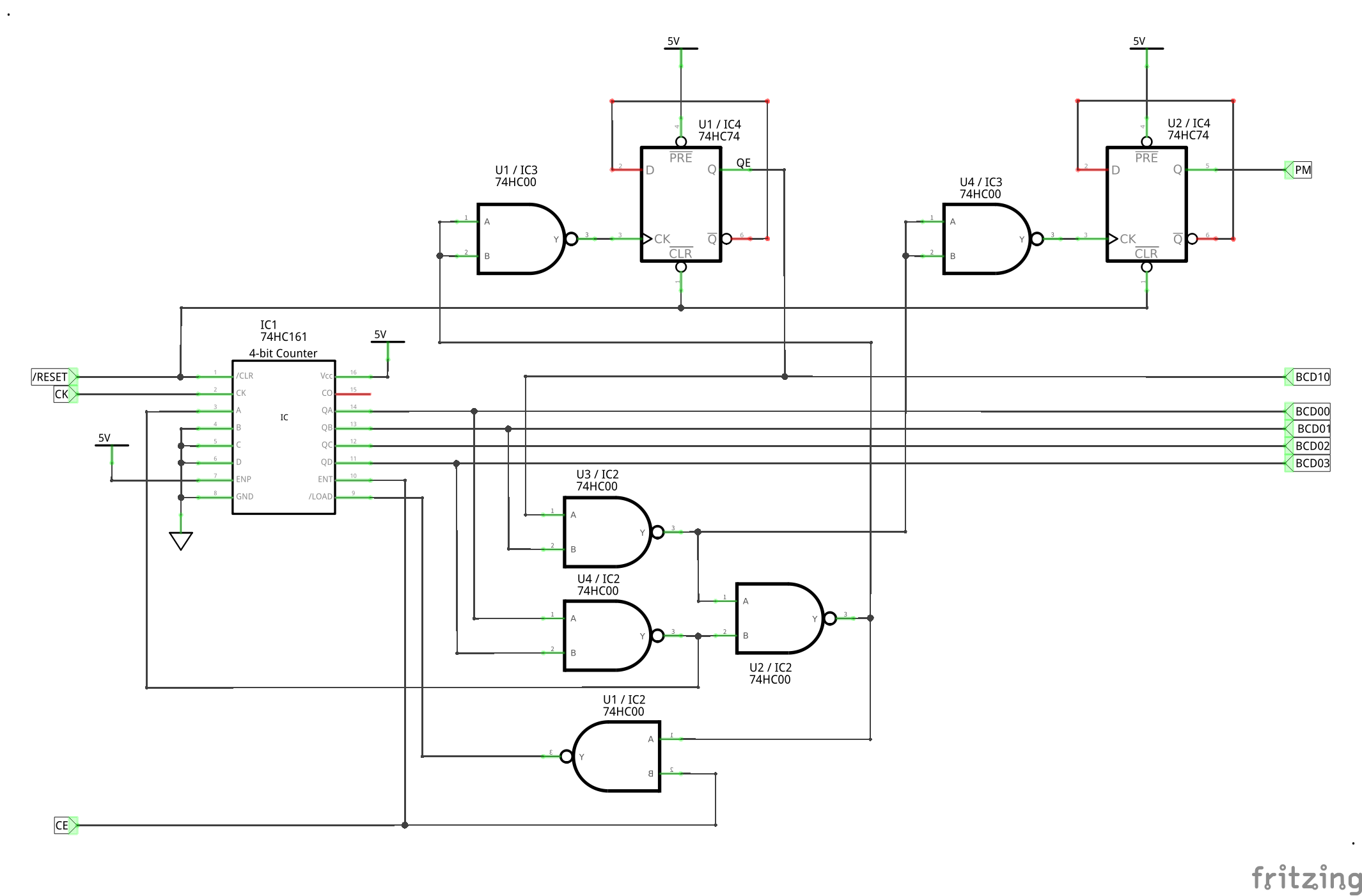

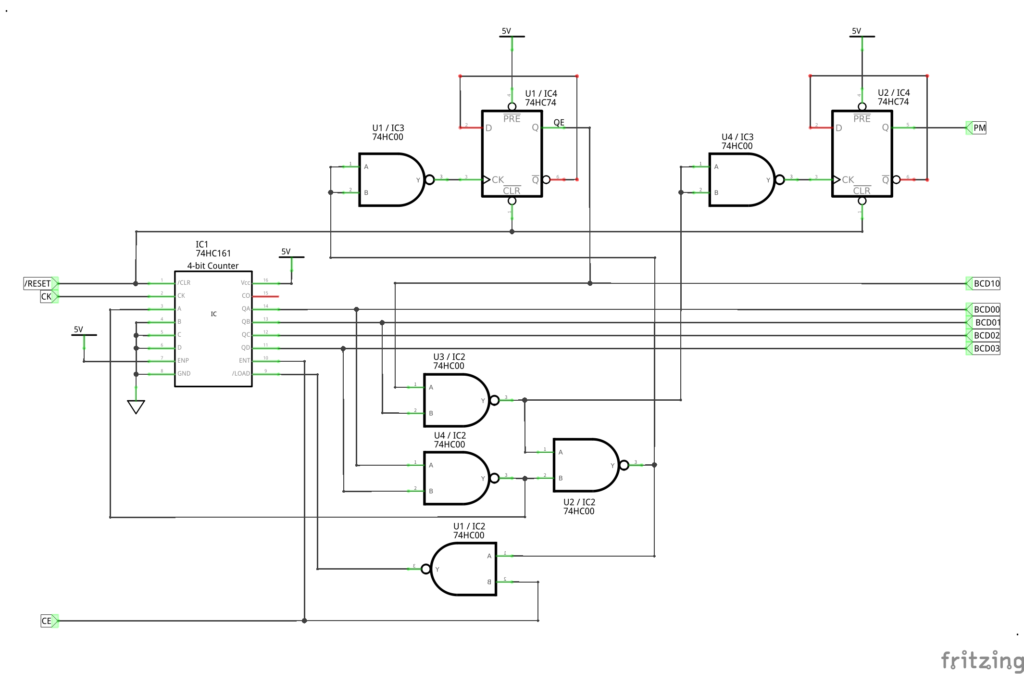

回路図

図1 が、時刻用 12進カウンタの回路図です。時刻表示は、以前と同様に 12時間計とし、午後信号 (12時~11時) を出力します。まぁ Q を取り出せば午前信号にもなるんですけどね。

左は 4bit 同期カウンタIC 74HC161A。1の位の BCD データ 4bit を出力します。

中央上が Dフリップフロップ 74HC74A で、10の位を出力します。10位は 0 か 1 だけなので、非同期のトグル動作にしています。

右上も Dフリップフロップ 74HC74A で、午後の信号を出力します。これも表示切り換えだけなので、非同期のトグル動作にしています。

組み合わせ回路を構成する

IC1 (4bit 同期カウンタ 74HC161A) と、組み合わせ回路 IC2 (NANDゲート 74HC00) は、1の位のカウンタを構成します。

時表示は、1、2 … 9、10、11、12、1、2 … と遷移します。そこで、1の位の出力が 0x9 のときに 0x0 をロードし、その他のときは 0x1 をロードすることにします。プリセットデータの LSB は入力 A ですので、

A = QD⋅QA

B、C、D は 0 に固定、つまり GND に接続しておきます。

ロードさせるタイミングは、カウントイネーブルで、出力が 0x09 のときと 0x12 のときです。したがって LD は、

LD = (QD⋅QA + QE⋅QB)⋅CE

となります。ここで QE は 10の位の出力、CE は下位カウンタからのキャリー (カウントイネーブル) 信号です。

10の位の切り換えは、出力が 0x09 と 0x12 で行ないます。切り換え信号を CA とすると、

CA = QD⋅QA + QE⋅QB

これを U1/IC4 (Dフリップフロップ 74HC74A) のクロックとして入力し、トグル動作させています。カウンタ回路と考えるなら同期させるべきかもしれませんが、ここは簡単にすませることにしました。

ちなみに、信号を反転させているのは、次のクロックで動作させるためです。

午前/午後切り換え信号は、出力が 0x12 になったときにトグルするようにします。午前/午後切り換え信号を SA とすると、

SA = QE⋅QB

こちらは U2/IC4 (Dフリップフロップ 74HC74A) のクロックとして入力します。上にも書きましたが、出力 Q は午後を、Q は午前を表示する信号になります。回路図には午後信号しか取り出していないです。

以上の論理式にしたがって回路図を作成していますが、すべてを NAND ゲートにするために、論理式を少し変形してます。さほど難しい変形ではないので、比較してみればすぐにわかると思います。

VerilogHDL によるシミュレーション

VerilogHDL で動作を確認してみます。

IC をモジュールにする

使っている IC をモジュールにしておくと便利かなと思うので、4bit 同期カウンタ 74HC161A と Dフリップフロップ 74HC74A をそれぞれ記述しておくことにします。

74HC161A はこれまでも使ってきた回路記述です。変更はありません。

- module TC74HC161A (

- input wire CK, CLR, LD, ENT, ENP,

- input wire [3:0] PRE,

- output reg [3:0] Q,

- output wire CO

- );

- always @(posedge CK, negedge CLR) begin

- if(1'b0 == CLR) begin

- Q <= 4'h0;

- end

- else if(1'b0 == LD) begin

- Q <= PRE;

- end

- else if(1'b0 == ENT || 1'b0 == ENP) begin

- end

- else begin

- Q <= Q + 4'h1;

- end

- end

- assign CO = (1'b1 == ENT && 4'hf == Q);

- endmodule

74HC74A を新たに記述しました。

プリセット PR とクリア CLR の動きでちょっと未確認なところがあるのですが、まぁ通常の動作に影響はないと思います。そのうち、気が向いたら確認します。

- module TC74HC74A (

- input wire D, CK, PR, CLR,

- output reg Q, NQ

- );

- always @(posedge CK, negedge PR, negedge CLR) begin

- if(1'b0 == CLR) begin

- if(1'b0 == PR) begin

- Q <= 1'b1;

- NQ <= 1'b1;

- end

- else begin

- Q <= 1'b0;

- NQ <= 1'b1;

- end

- end

- else if(1'b0 == PR) begin

- Q <= 1'b1;

- NQ <= 1'b0;

- end

- else begin

- Q <= D;

- NQ <= ~D;

- end

- end

- endmodule

12進カウンタの動作シミュレーション

12進カウンタの回路を記述します。

10行目の PRE はプリセットデータですが、A だけでなく 4bit で扱って、セレクタで切り換えています。あとは上の論理式にしたがって記述し、下位モジュールとして IC を接続しています。

- module COUNTER_MOD12 (

- input wire CK, RESET, CE,

- output wire [3:0] Q0,

- output wire Q1, PM

- );

- wire [3:0] PRE;

- wire LD, CA, SA;

- assign PRE = (Q0[3] & Q0[0]) ? 4'h0 : 4'h1;

- assign LD = ~((Q0[3] & Q0[0] | Q1 & Q0[1]) & CE);

- assign CA = ~(Q0[3] & Q0[0] | Q1 & Q0[1]);

- assign SA = Q1 & Q0[1];

- TC74HC161A U0(CK, RESET, LD, CE, 1'b1, PRE, Q0, CO);

- TC74HC74A U1(NQ1, CA, 1'b1, RESET, Q1, NQ1);

- TC74HC74A U2(NQ2, SA, 1'b1, RESET, PM, NQ2);

- endmodule

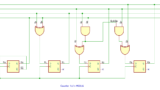

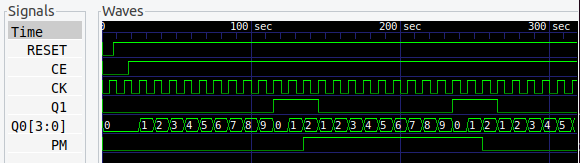

図2 が、シミュレーションの結果です。

じっさいの回路では、3600 クロックごとに CE が HIGH になり、そのときにカウントアップするように動作します。が、ここでは、クロックをカウントして、出力の遷移が想定通りになるかどうかを確認しています。

Q0 は 1の位の 4bit BCD 出力。Q1 は、HIGH のとき 10の位を 1 としています。なお、電源オン時などリセットしたときは 0 からスタートし、1 へ遷移します。12 に初期化させるには、そのための回路が必要になるので、やめました。どうせ時刻合わせしないといけないし、いいでしょ。

午後信号は、12〜11 で出力します。午前 0時は「午前12時」、正午は「午後12時」となります。

後記

今回は、デジタル時計の時表示用の 12進カウンタをつくりました。

1 から始まって 12 で終わる、時表示って悩ましいですよねぇ。

以前フリップフロップでやったときは、5bit カウンタ BCD 出力で設計しました。単純に 0x1〜0xC を出力して、9セグメントへデコードするって手もあります。あっさり 24時間計にしちゃえば簡単かもしれない。

今回の回路も、10の位にも 74HC161A 使ったほうがきれいだったかもしれません。

ま、いろんな方法があると思いますが、基本、部品箱にあるものを使おうってのは、いつも同じです。

さてと、カウンタ部分ができましたので、これ、デジタル時計にしましょう。次回から、周辺の回路をつくっていきます。

74HC161A / 4bit 同期バイナリカウンタIC を使ってみる

74HC161A / イネーブル付き 10進カウンタをつくる

74HC161A / 同期 60進カウンタをつくる

74HC161A / 時表示用 12進カウンタをつくる

74HC161A / 時計用の 2Hzクロックをつくる

74HC161A版 デジタル時計 / 時刻合わせ回路

74HC161A版 デジタル時計 / 7セグLED表示回路(仮)

74HC161A版 デジタル時計 / カウンタ部を基板に組む

74HC161A版 デジタル時計 / バイナリ表示器をつくる

74HC161A版 デジタル時計 / 7セグメントLED 表示器をつくる

74HC161A版 デジタル時計 / リングLED 表示器をつくる