2つ目の例題です。

【問題2】 4ビット加算器をVerilog HDLで記述しよう

今回は、Verilog HDLの記述スタイルについて解説。回路は“モジュール”の枠に収めて定義し、信号は“ポート”として定義する。

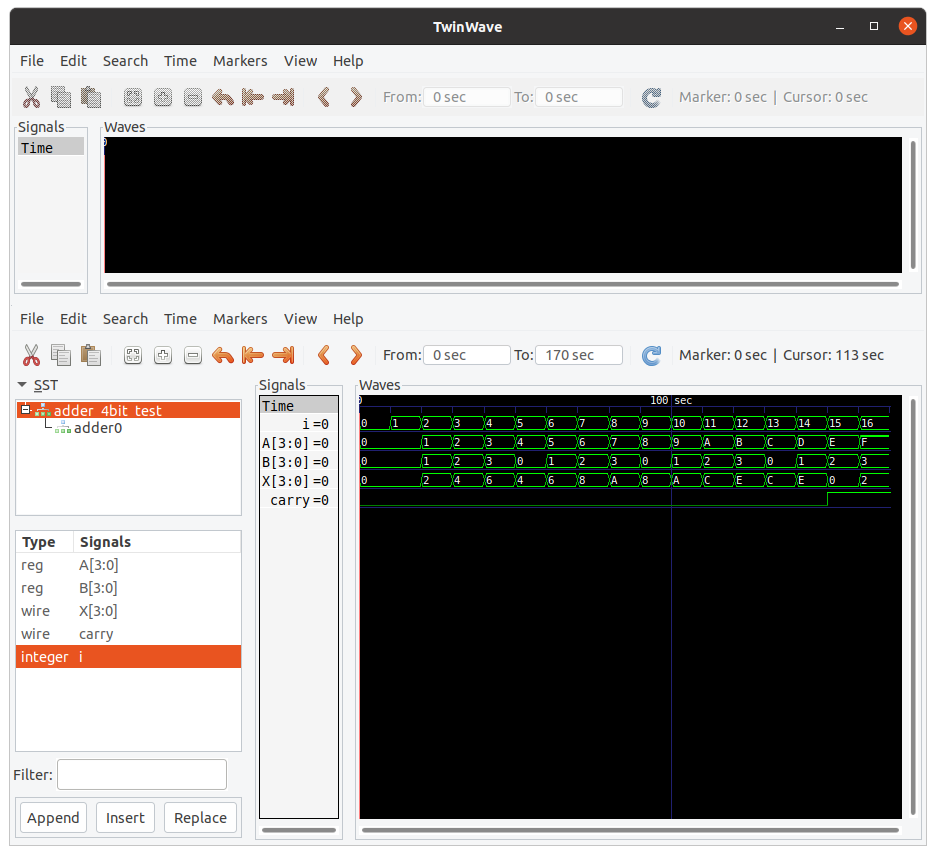

4 ビット加算器をシミュレーションする

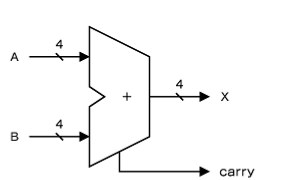

図 1 に示す、4 ビット加算器のシミュレーションをしましょう。

論理回路のおさらいに、加算器はまだ登場してませんけど、むずかしいもんじゃないです。4 ビット加算器なら、4 ビットのデータ A と B を足し算するだけ。桁上がりすると carry (1 ビット) が出力される。

あー、でも、ロジック IC で 4 ビット加算器をつくるのは、それなりに大変、か (;´Д`)

回路記述

回路をつくります。

- module adder_4bit(A, B, X, carry);

- input [3:0] A, B;

- output [3:0] X;

- output carry;

- wire [3:0] A, B, X;

- wire carry;

- assign {carry, X} = A + B;

- endmodule

基本的には、組み合わせ回路とおなじです。

A、B、X は、それぞれ 4 ビットなので、[MSB:LSB] ってふうにして 4 ビットの信号を表します。

9 行目が、加算器をつくる記述。{carry, X} は、信号を連結する記述、だそうです。

テストベンチ

テストベンチファイルです。

- module adder_4bit_test;

- integer i;

- reg [3:0] A, B;

- wire [3:0] X;

- wire carry;

- adder_4bit adder0(A, B, X, carry);

- initial begin

- A = 4'b0; B = 4'b0;

- for(i = 0; i < 16; i=i+1)begin

- #10 A = i; B = i % 4;

- end

- #10 $finish;

- end

- initial begin

- $monitor("%d + %d = %d", A, B, X);

- $dumpfile("adder_4bit_test.vcd");

- $dumpvars(0, adder_4bit_test);

- end

- endmodule

3 行目。for() 文のループ変数の宣言。C 言語みたいに for() 文のなかでは、できない、みたい。

12 行目。定数は「4’b0」のように記述する。「4 桁の 2 進数 (b) の 0」って意味です。

13 行目。for() 文。i++ も使えない、みたい。処理内容は begin と end でくくられる。C 言語だと {} だね。

14 行目。10 ユニット時間ごとに実行する内容。A は 0~15 を、B は 0~3 を繰返し、これを入力としてみました。お好みで。入力をどうするか、ってのは、シミュレーションのためのポイントかな。