VerilogHDL と GTKWave の環境が整いましたので、いくつか例題を試してみようと思います。以下のサイトの問題を、例題にさせていただきました。

【問題1】 Verilog HDLをマスターしよう!!

「完全マスター! 電子回路ドリル」の3学期がスタート! “ハードウェア記述言語”をテーマにさまざまな問題を毎週お届けします。

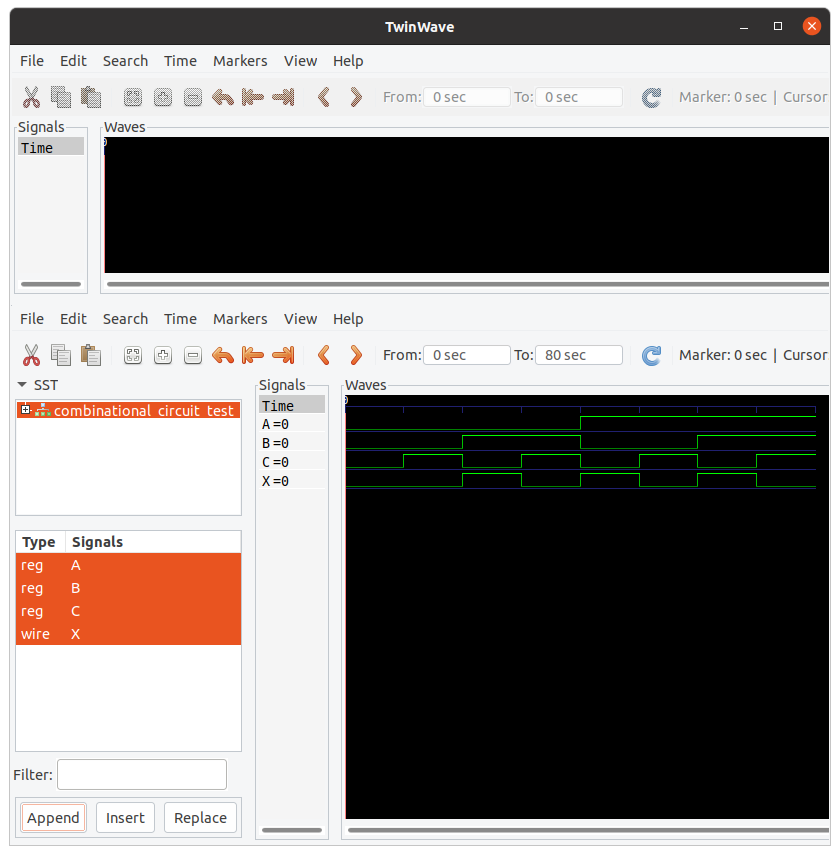

組み合わせ回路をシミュレーションする

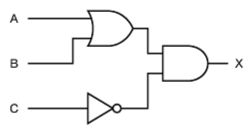

組み合わせ回路です。

まぁ、簡単ですね、みればわかる (^_^;)

A または B のどちらか、もしくは両方が 1 のときに、C が出力される回路です。

これをシミュレーションしてみましょう。

基本は、準備編でやった AND 回路とおなじです、入力が 3 つになっただけ。

回路記述

まずは、回路をつくります。

- module combinational_circuit(A, B, C, X);

- input A, B, C;

- output X;

- wire A, B, C, X;

- assign X = ( A | B ) & ~C;

- endmodule

AND 回路のときと同じなので、説明は省略 m(__)m

テストベンチ

つぎに、テストベンチファイル。

- module combinational_circuit_test;

- reg A, B, C;

- wire X;

- combinational_circuit comb_ckt0(A, B, C, X);

- initial begin

- A=0; B=0; C=0;

- #10 C=1;

- #10 B=1; C=0;

- #10 C=1;

- #10 A=1; B=0; C=0;

- #10 C=1;

- #10 B=1; C=0;

- #10 C=1;

- #10 $finish;

- end

- initial begin

- $monitor("A=%d, B=%d, C=%d, X=%d", A, B, C, X);

- $dumpfile("comb_ckt_test.vcd");

- $dumpvars(0, combinational_circuit_test);

- end

- endmodule

信号の入力は、変化するところだけ記述すればいいですね。コンソール出力が不要なら、21 行の $monitor は不要です。が、波形ファイルを生成するために、vvp は実行しないといけません。