カウンタ回路で遊びつかれたので (;´Д`)、ちょっと違うことをしようかな。といっても、論理回路つながりで、VerilogHDL を勉強してみようと思います。

まぁ、FPGA とか使うつもりはないんだけど、パソコン上でシミュレーションできるのは便利かな、と。Arduino と同様に、俺がちょっとだけ電子回路さわっていた 40 年ほど前にはなかったものだし、ちょっとだけの技術的な興味です。

まいどまいどですが、VerilogHDL が何ものか、についてはググって下さいませ m(__)m

環境の準備

シミュレータ環境のインストール

俺のパソコンの OS は ubuntu 20.04.5 LTS です。こいつに、波形データを作成するためのシミュレータ「IcarusVerilog」と、波形を表示する「GTKWave」をインストールします。

インストールは、ターミナルから以下のコマンドで。GUI なら、Synaptic パッケージマネージャからでもいいです。

sudo apt install iverilog sudo apt install gtkwave

AND 回路をつくる

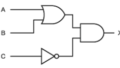

シミュレータを試してみるために、AND 回路を VerilogHDL で記述してみましょう。

まずは、回路の部品にあたるモジュールをつくります。

- module andGate(A, B, Y);

- input A, B;

- output Y;

- wire A, B, Y;

- assign Y = A & B;

- endmodule

C 言語に影響を受けているらしいので、C 言語のような書き方ですね。

1 行目。モジュール名 andGate で、モジュールを定義します。() 内にポート名を記述します。

2 行目が入力ポート、3 行目が出力ポートの宣言。

5 行目は、モジュール内で使う信号の宣言、だそうです。wire で宣言すると「信号線」を意味する。いまいち、わかりませんケド (;´Д`)

7 行目が回路機能の宣言。回路を論理式で表せるときは assign 文をつかう、と。AND ゲートなので、論理式は Y = A・B ですね。

最後に endmodule で定義を終了します。

テストベンチファイルの作成

テストベンチファイルは、上でつくった AND 回路に信号を入れて、動作させるためのプログラムファイルです。これも VerilogHDL で記述します。

- module andTest;

- reg A, B;

- wire Y;

- andGate and0(A, B, Y);

- initial begin

- A = 0; B = 0;

- #10 A = 1; B = 0;

- #10 A = 0; B = 1;

- #10 A = 1; B = 1;

- #10 A = 0; B = 0;

- #10 $finish;

- end

- initial begin

- $monitor("A = %d, B = %d, Y = %d" , A, B, Y);

- $dumpfile("andTest.vcd");

- $dumpvars(0, andTest);

- end

- endmodule

テストベンチも module で始まって、endmodule で終わります。

1 行目はモジュール名。andTest としました。

3~4 行目。reg は信号を印加するポート、wire は出力を観測するポート、だそうです。

6 行目。モジュール andGate をインスタンス化して and0 を生成する。そうそう、C++ クラスでそんなのやったですねぇ。オブジェクト指向プログラミング、ってやつ。

8~15 行は、テスト信号の作成です。initial begin で始まって、end で終わる。

まず A=0、B=0 を入力に印加。#10 は 10 ユニット時間の遅延、遅延時間後に A=1 にする。さらに 10 ユニット時間後に、A=0、B=1 にする。そして、A=1、B=1 にする。ふむ、真理値表の状態遷移をいれてみればいいんだな。

$finish でシミュレーション終了。

17~21 行は、観察する信号の指示です。

$monitor は、信号の値をコンソールに出力する。つまり、ディスプレイに表示する、ってこと。

$dumpfile は、波形データのファイル名の指定。$dumpvars は、レベルとモジュールの指定。ここでは、モジュール andTest を、ファイル名 andTest.vcd で出力することになる。レベル?ん、わかんないけど、0。

理解できそうなところ、よくわかんないところ、いろいろあるけど、とりあえず準備完了。

シミュレーション波形表示

回路をつくり、テストベンチを用意したので、シミュレーションしてみましょう。

コンパイル

まず、シミュレーションのためのオブジェクトファイルをつくります。C 言語などのプログラムとおんなじですねぇ。

iverilog -o andTest.out andGate.v andTest.v

-o オプションは出力ファイル名。省略すると a.out になります。

シミュレータの起動

シミュレータで、生成されたオブジェクトファイルを起動すると、$monitor で指定されたコンソールに、結果が出力されます。

vvp andTest.out VCD info: dumpfile andTest.vcd opened for output. A = 0, B = 0, Y = 0 A = 1, B = 0, Y = 0 A = 0, B = 1, Y = 0 A = 1, B = 1, Y = 1 A = 0, B = 0, Y = 0

お、たしかに AND ゲートの入出力が表示されましたよ。うまくいったようです。

波形の確認

vvp コマンドを実行すると、$dumpfile で指定した波形ファイル andTest.vcd が生成されます。これを GTKWave で表示させます。

twinwave + andTest.vcd

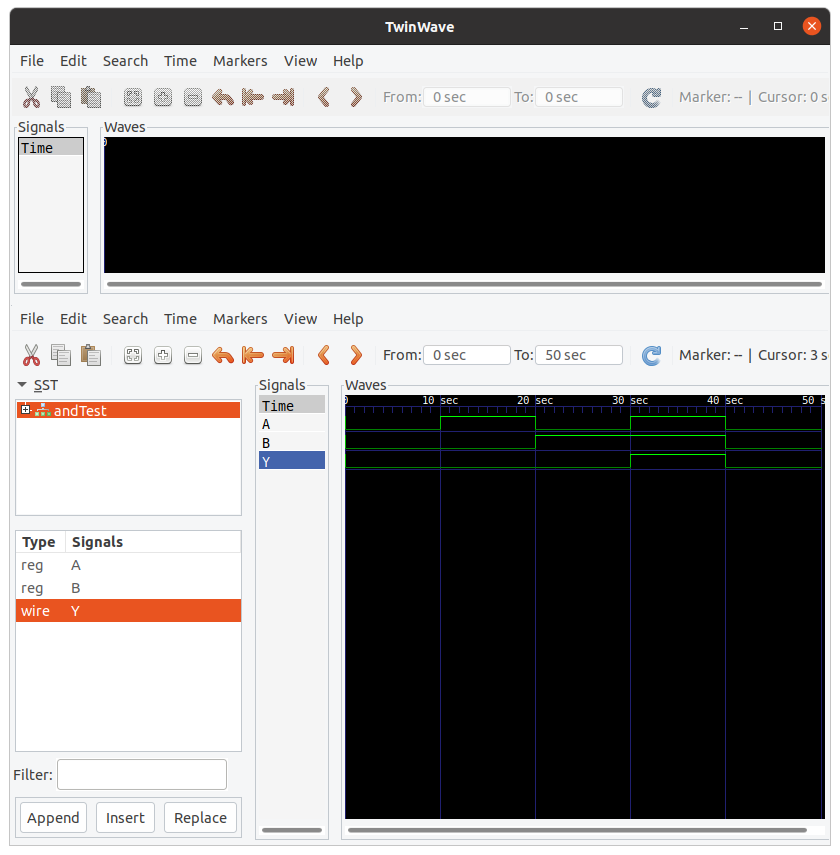

GUI のアプリケーションが起動しましたが、ん? TwinWave ってアプリケーション?

SST にあるandTest をクリックすると、下に Signals が表示されます。選択して Append ボタンを押すと、Waves に信号が追加されます。

操作方法? よくわからんです (;´Д`) まぁいろいろさわっているうちに、わかってくるでしょう。

ちなみに、

twinwave ++ andTest.vcd

と起動すると、GTKWave で二画面に分割されて起動します。TwinWave は、複数の GTKWave を 1 つ、または 2 つのウインドウで開く、ものらしいです。

エラーへの対処

とりあえず GTKWave が動きましたが、ターミナルにエラーがでています。

Gtk-Message: 19:44:04.359: Failed to load module "canberra-gtk-module"

こいつを消すには、ライブラリをインストールすればよいそうです。

sudo apt install libcanberra-gtk*

ということで、エラーはすっきり消えました。

後記

「HDLとは」ってググると、善玉コレステロールがでてきます (^_^;) 検索は「HDL言語」とかでどうぞ。

HDL には、VerilogHDL と VHDL があるそうですが、別物だそうです。VHDL は VerilogHDL を略したものではないんです。まぎらわしい。

で、よくわからんのですが、SystemVerilog ってのがあるらしい。VerilogHDL を改良したものらしいんですけど、バージョンアップされたもの、とは違う? C と C++ みたいな?

多くの Google 先生に教えていただきました。特に、下記のサイトがたいへん参考になりました。ありがとうございます。