一般に、カウンタ回路は同期式が利用されている。非同期式は、回路の遅延のばらつきが大きく、動作が不安定になりやすい。同期式は、回路が複雑になるが、動作が安定している。

ってことで、同期カウンタ回路を勉強しましょう。

なお、多くのグーグル先生にたくさん、いろいろ教えていただきました。なかでも、

Hatada’s Home Page

3 bit synchronous up counter using j k flip flop | counters

は、とても参考になりました。ありがとうございます。

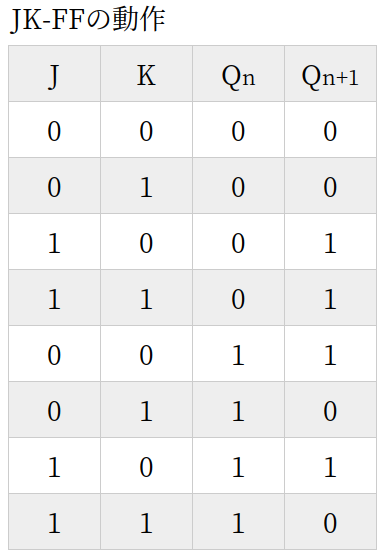

JKフリップフロップの動作

まず、JKフリップフロップの動作をおさらいします。

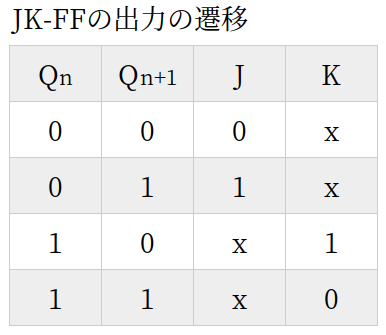

図 1 は、JKフリップフロップの動作を表しています。J、K は入力の状態。Qn は現在の出力、Qn+1 は次の出力の状態です。

たとえば 3 行目、入力が (1,0) で、Qn=0 のとき、Qn+1 は 1 に変化します。入力が同じ (1,0) であっても、7行目のように、Qn=1 のときは、Qn+1 は変化しません。

JKフリップフロップ の動作を、出力の遷移を視点にしたのが、図 2 です。

出力が 0 → 1 に変化するのは、J=1 のときで、K は don’t care です。同様に、出力が 1 → 0 に変化するのは、K=1 のときで、J は don’t care です。

don’t care とは、0 でも 1 でもかまわない、ということです。

JKフリップフロップは、Qn=0 のときは入力 J によって、Qn=1 のときは入力 K によって、次の出力が変化する、ということがわかります。

JKフリップフロップを使った 4進同期カウンタ

とりあえず、回路の構成が簡単な 4進同期カウンタで実験してみました。

そのあとで、回路の設計をやりましょう。JKフリップフロップを使った、同期式のアップ・バイナリ・カウンタを基準とします。

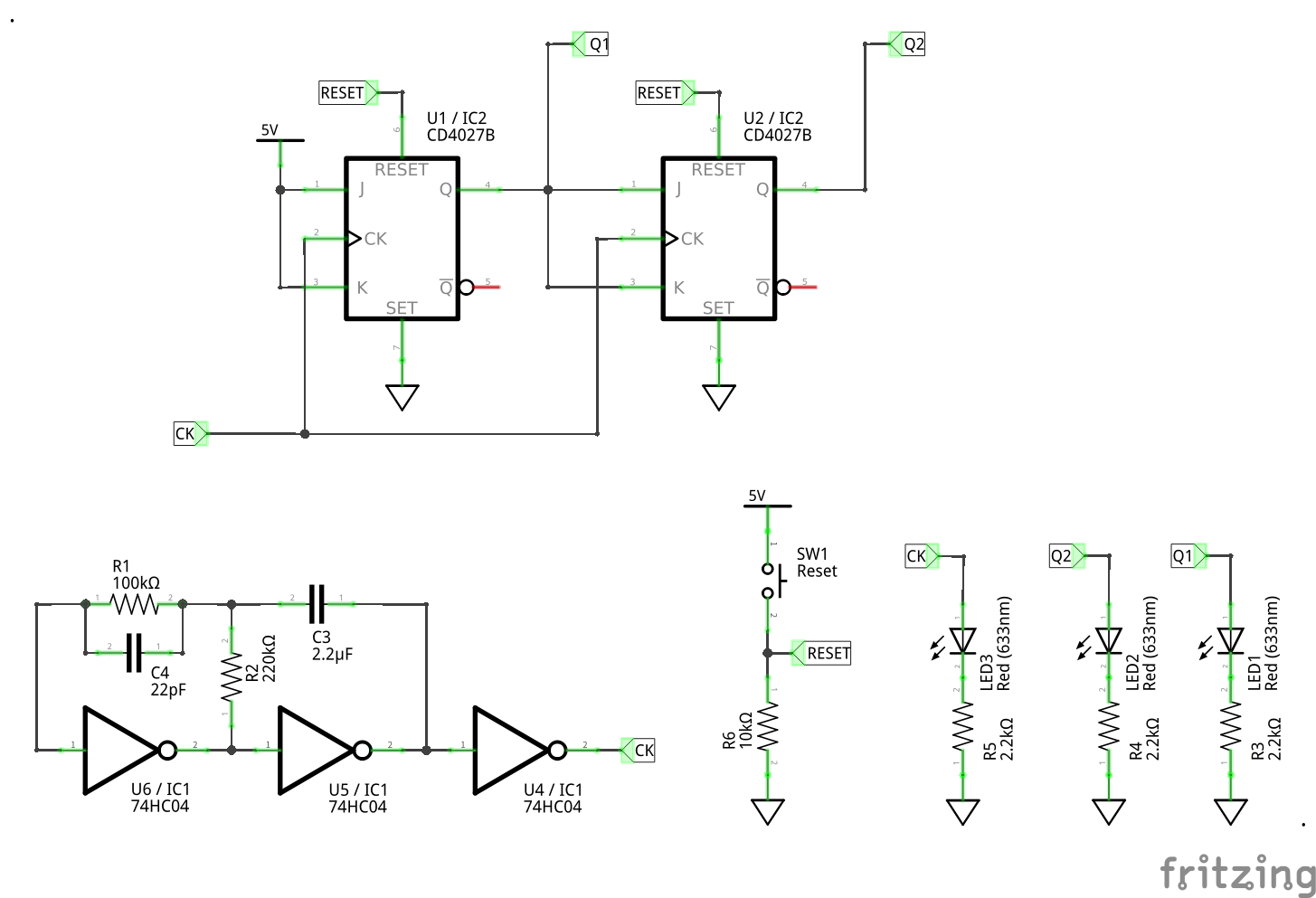

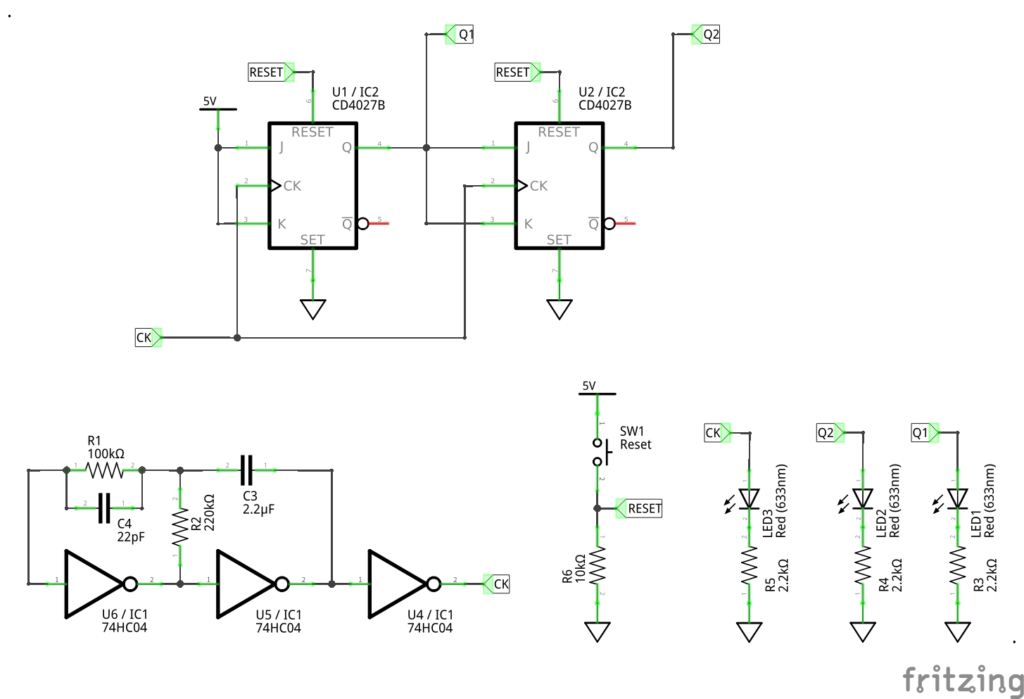

実験回路図

上側が、JKフリップフロップ 2段で構成した 4進同期カウンタです。各 JKフリップフロップには、同一のクロックが入力されている、つまり「同期」しています。

左下はクロックの発振回路、右下が、リセットスイッチ SW1、クロックの表示 LED3 と、出力表示 LED1、LED2 です。LED1 が LSB、LED2 が MSB になっています。

LED1、LED2 は、

00 → 01 → 10 → 11 → 00 → …

のように、カウント表示していきます。出力が 2 ビットなので、クロックの数を 22 で割った余り 0 から 3 が表示される仕組みです。

4進同期カウンタの設計

さてと、頭が痛くなりますが、回路の設計方法をまとめておきましょう。

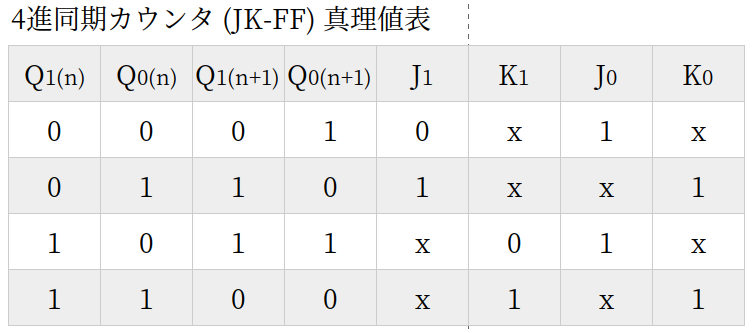

図 4 が 4進同期カウンタの真理値表です。

Q1(n)、Q0(n) は、ビット 1 とビット 0 の現在値。00 から 11 まであります。

Q1(n+1)、Q0(n+1) は、次の出力の状態。n のとき 00 ならば、n+1 は 01 ですから、01 から 00 までとなります。

J1、K1 は、ビット 1 の入力です。ここは、Q1(n) → Q1(n+1) の変化に着目します。

1 行目。Q1(n)=0 が Q1(n+1)=0 になります。図 2 から、このときは J1=0、K1=x です。

2 行目。同様に、Q1(n)=0 が Q1(n+1)=1 になりますから、図 2 から J1=1、K1=x です。

3 行目は、Q1(n)=1、Q1(n+1)=1 なので J1=x、K1=0

4 行目は、Q1(n)=1、Q1(n+1)=0 なので J1=x、K1=1

これで、J1、K1 の列が埋まりました。

J0、K0 は、ビット 0 の入力です。ここは、Q0(n) → Q0(n+1) の変化をみます。

1 行目は、 Q0(n)=0、Q0(n+1)=1 なので J0=1、K0=x です。

以下、同様にして、J0、K0 を埋め、真理値表が完成しました。

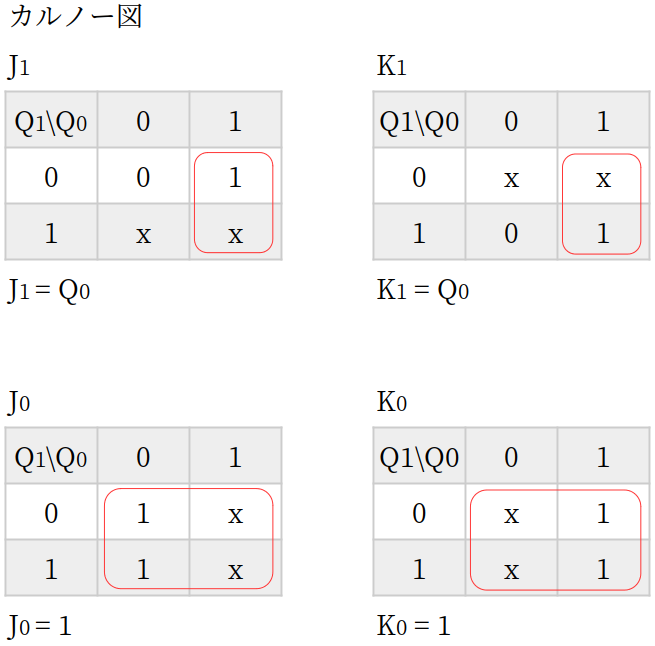

真理値表にしたがい、カルノー図を描きます。

J1 について。

Q1Q0 が 00 のとき、J1 は 0 ですので、左上のマスには 0 を書き入れます。Q1Q0 が 01 のとき、J1 は 1 なので、右上のマスには 1 を書き入れます。同様に、Q1Q0 が 10 のとき J1 は don’t care、Q1Q0 が 11 のとき J1 は don’t care です。

1 を囲んだ赤色のループより、論理式は J1=Q0 となります。

K1 について。

Q1Q0=00 のとき K1=x

Q1Q0=01 のとき K1=x

同様に、10 のとき K1=0、11 のとき K1=1 となり、論理式は K1=Q0 となります。

以下、同様にカルノー図を描き、論理式を求めた結果、

J1 = Q0 K1 = Q0 J0 = 1 K0 = 1

となりました。

この論理式から論理回路をつくると、図 3 のカウンタ回路部分になります。

JKフリップフロップの 1 段目 (ビット 0) の入力 J0、K0 は常に 1 ですので、5V ラインにつないでおきます。2 段目 (ビット 1) の入力 J1、K1 はともに Q0 ですので、1 段目 (ビット 0) の出力 Q0 につなぐ。

ということです。

後記

4進同期カウンタは、JKフリップフロップだけで構成できるので、とても簡単でした。

が、設計方法は何進であっても同じ。ビット数が多くなれば、それだけ多くの真理値表、カルノー図を作らなければなりませんが、それはせっせと手を動かせば済むことなので、問題はないです。

とうぜん設計するためのツールがあるんだろうと思いますが、趣味で回路を考えるのですから、こういう計算も、また楽しい、あ〜頭痛いけど、ものです。

論理回路 / 基本的な論理回路

論理回路 / RSフリップフロップ

論理回路 / ゲート型 RS フリップフロップ

論理回路 / プライマリ・レプリカ型 RS フリップフロップ

論理回路 / Dフリップフロップ

論理回路 / JK フリップフロップ

論理回路 / 分周回路・カウンタ回路

論理回路 / 4進同期カウンタ (2bit)

論理回路 / 8進同期カウンタ (3bit)

論理回路 / 16進同期カウンタ (4bit)

論理回路 / 10進同期カウンタと 7セグメントLED

論理回路 / 半加算器と全加算器

論理回路 / 4ビット加算器の構成とシミュレーション

論理回路 / 4ビット加算器をロジック IC でつくる

加算器でカウンタを作る / 構成とシミュレーション

加算器でカウンタを作る / 16進カウンタ

加算器でカウンタをつくる / 10進カウンタ

論理回路 / シフトレジスタ・ジョンソンカウンタ・リングカウンタ

さらに…