前回は、JKフリップフロップを使った 3ビットの 8進同期カウンタを作ってみました。

今回は、もうひとつ増やした 4ビットの 16進カウンタを設計してみます。だんだん規模が大きくなっていきますが、基本は同じですので、難しくはないです。

JKフリップフロップを使った 16進同期カウンタ

4ビットなので、JKフリップフロップが 4個になります。が、3ビット目までは、8進同期カウンタとまったく同じ動きですから、4ビット目だけを追加して考えればいいです。

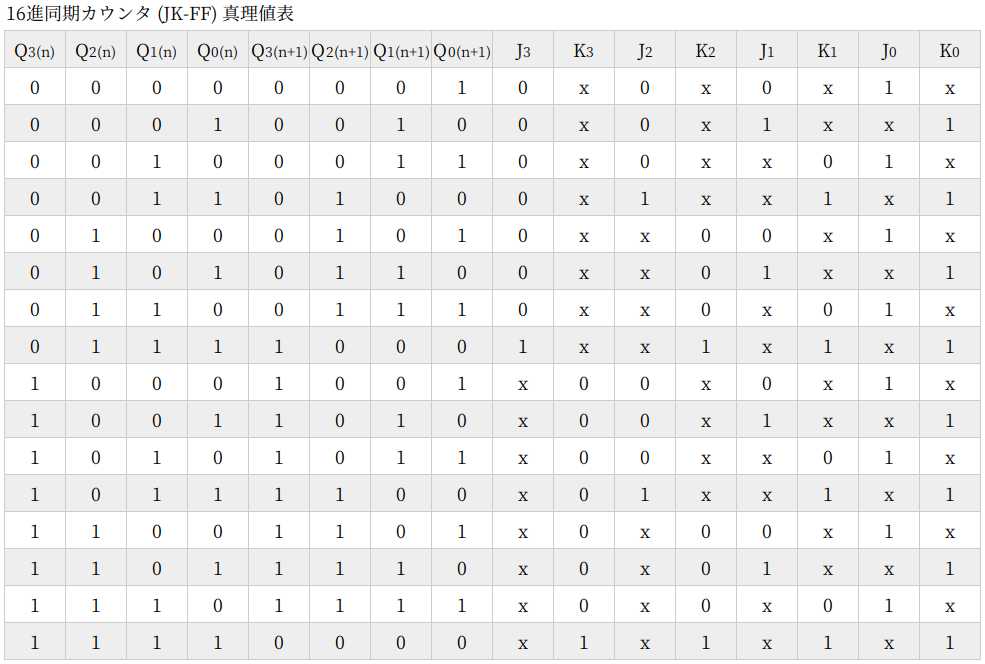

とはいっても、部分的な真理値表を作っても訳わかんなくなりますから、全体を書いておきます。

ちなみに、俺はこれをスプレッドシートで書いてます。4 ビット目について考えるときは、Q3(n)、Q3(n+1)、J3、K3 の列だけを表示させるようにしてます。わかりやすくなりますよ。

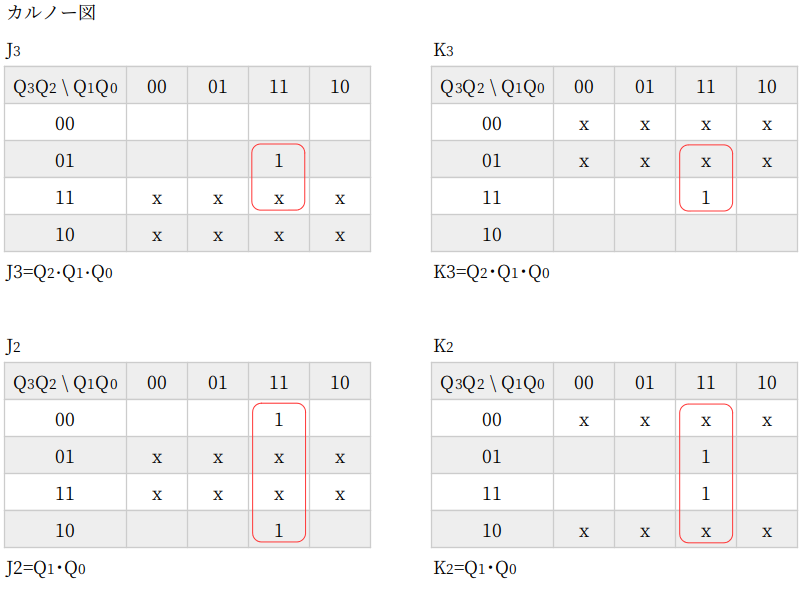

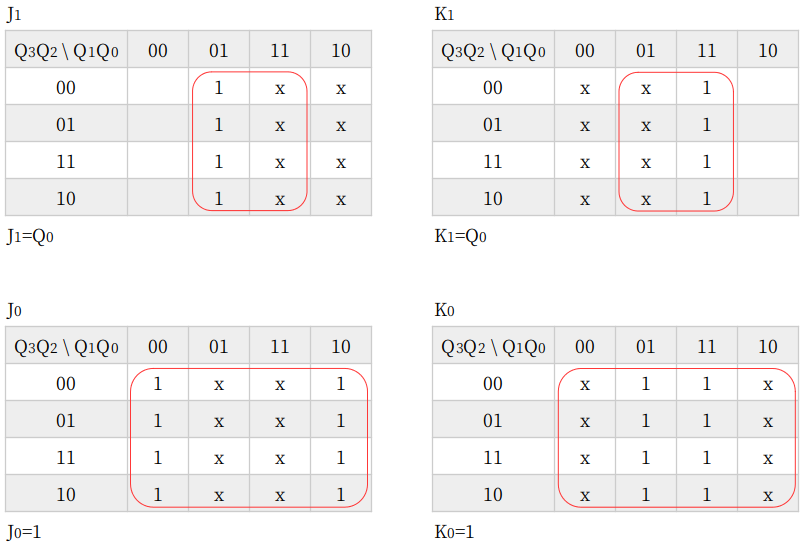

以下、これまでと同様、真理値表からカルノー図を描いて、論理式を求めます。

とうことで、論理式は次のようになりました。前述のとおり、3ビット目までは 8進同期カウンタと同じです。

J0 = K0 = 1 J1 = K1 = Q0 J2 = K2 = Q1・Q0 J3 = K3 = Q2・Q1・Q0 = Q2・J2

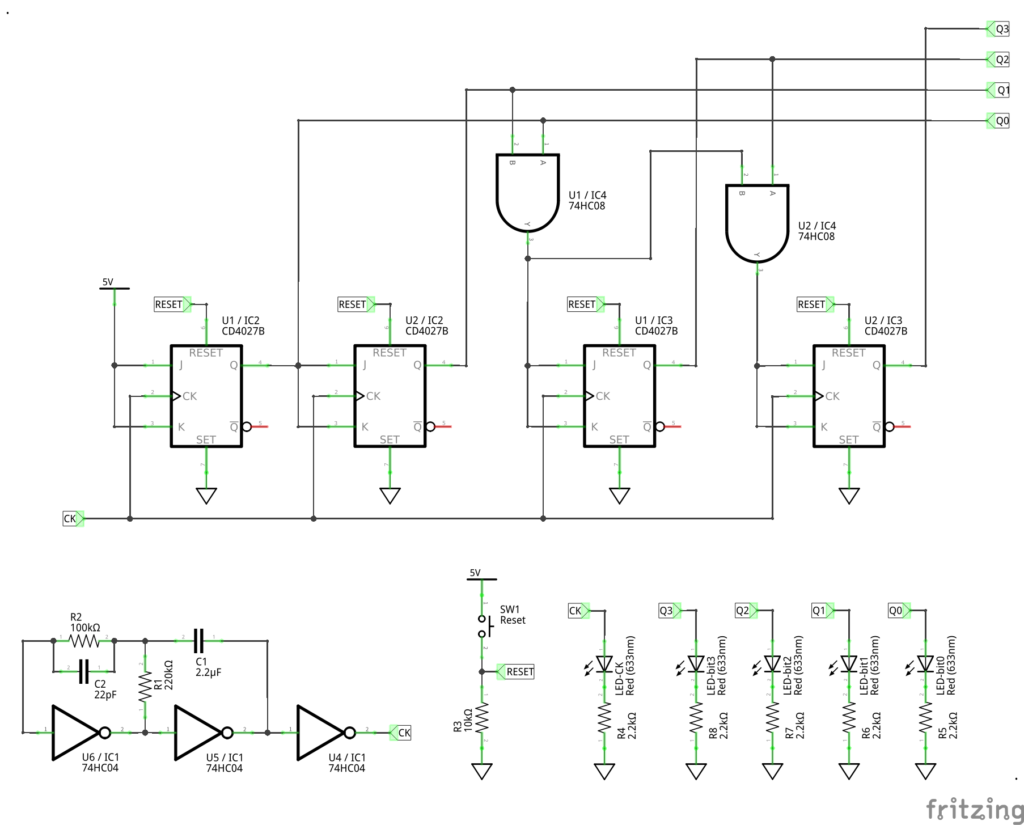

4ビット目 J3、K3 の入力ゲートについて、3入力 AND を使うこともできますが、3ビット目の AND 出力が利用できますね。2入力 AND ゲートが余っていますので、これを使いましょう。IC の数が節約できます。

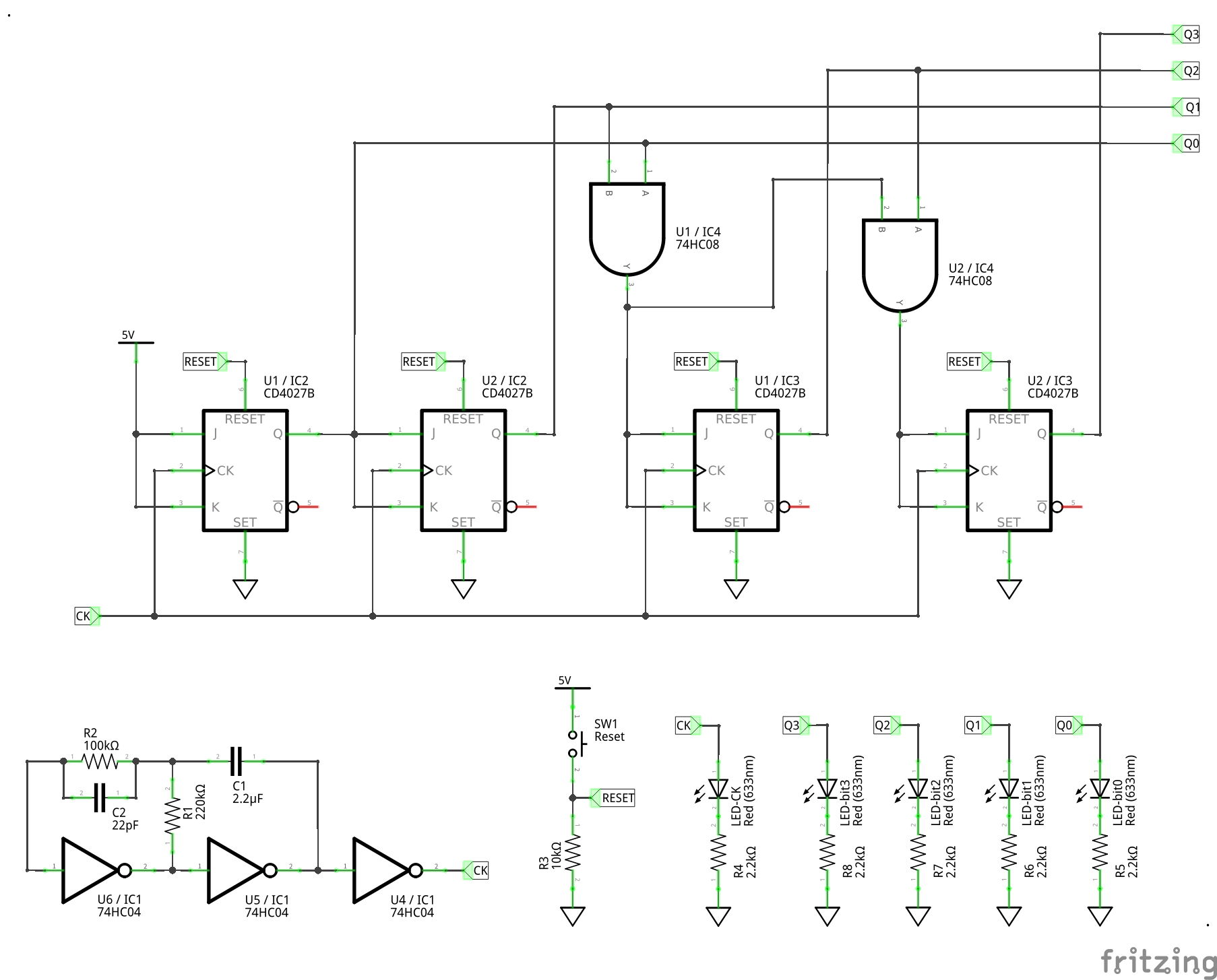

ということで、作ったカウンタ回路は図 3 のとおりです。

前回の 8進同期カウンタに、4ビット目の JKフリップフロップ、入力ゲート、出力 LED を追加しただけです。このカウンタも、出力を Q に変更すればダウン・カウンタに変わります。

後記

同期カウンタ回路の設計は、まぁこんなところですかねぇ。さらにビット数の多いカウンタになったら、ビット数だけ JKフリップフロップを並べて、ビットごとに入力ゲート回路を考えるのがいいように思います。用途によるけど、非同期式と同期式を合わせて使うとか、バイナリ・カウンタではない方法を使うとか、頭柔らかくして作ってみるのが楽しいと思います。

さて、基本的なところはこれくらいにして、何か作ってみようかな。ちょっと考えてみます。

論理回路 / 基本的な論理回路

論理回路 / RSフリップフロップ

論理回路 / ゲート型 RS フリップフロップ

論理回路 / プライマリ・レプリカ型 RS フリップフロップ

論理回路 / Dフリップフロップ

論理回路 / JK フリップフロップ

論理回路 / 分周回路・カウンタ回路

論理回路 / 4進同期カウンタ (2bit)

論理回路 / 8進同期カウンタ (3bit)

論理回路 / 16進同期カウンタ (4bit)

論理回路 / 10進同期カウンタと 7セグメントLED

論理回路 / 半加算器と全加算器

論理回路 / 4ビット加算器の構成とシミュレーション

論理回路 / 4ビット加算器をロジック IC でつくる

加算器でカウンタを作る / 構成とシミュレーション

加算器でカウンタを作る / 16進カウンタ

加算器でカウンタをつくる / 10進カウンタ

論理回路 / シフトレジスタ・ジョンソンカウンタ・リングカウンタ

さらに…