ロジック IC を使って、デジタル時計をつくっています。前回は、基準クロック発振回路として 32.768KHz の発振回路をつくってみました。

今回は、基準クロック回路として、この発振回路をデジタル時計に組み込んでいきます。

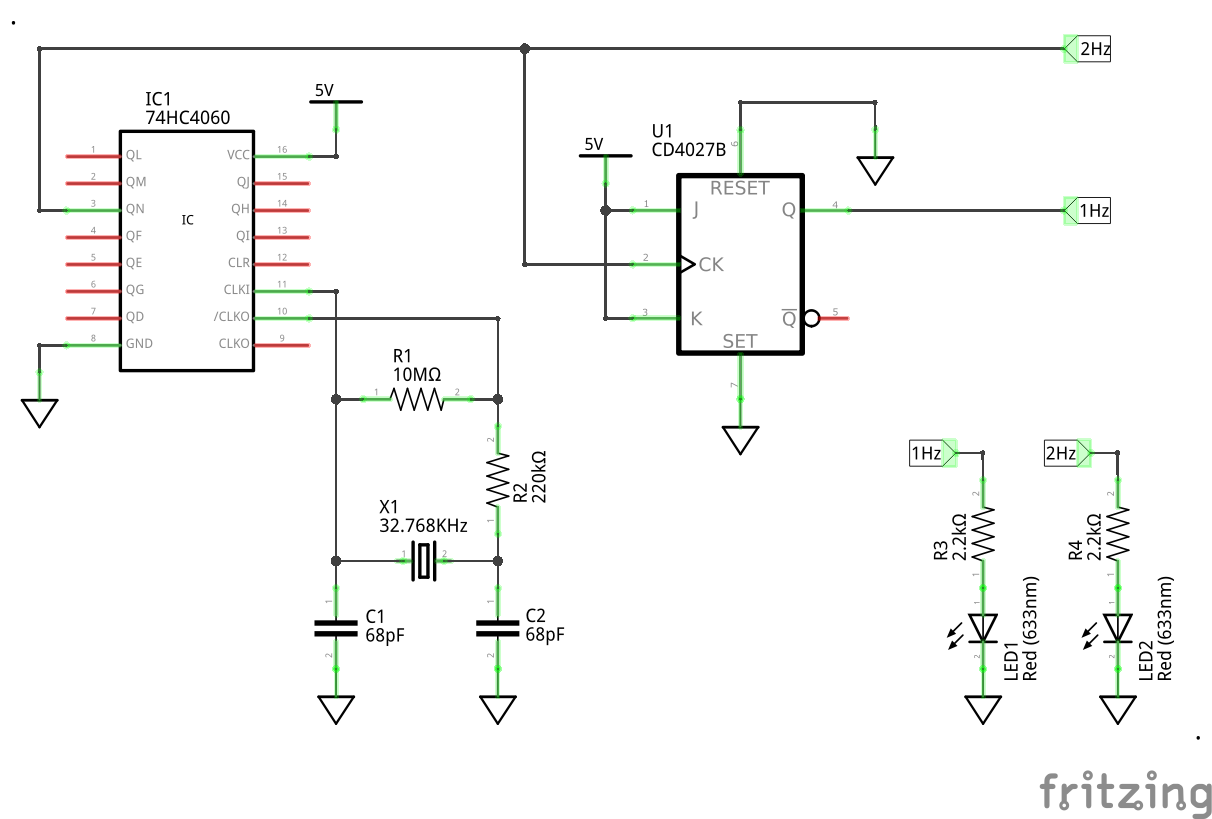

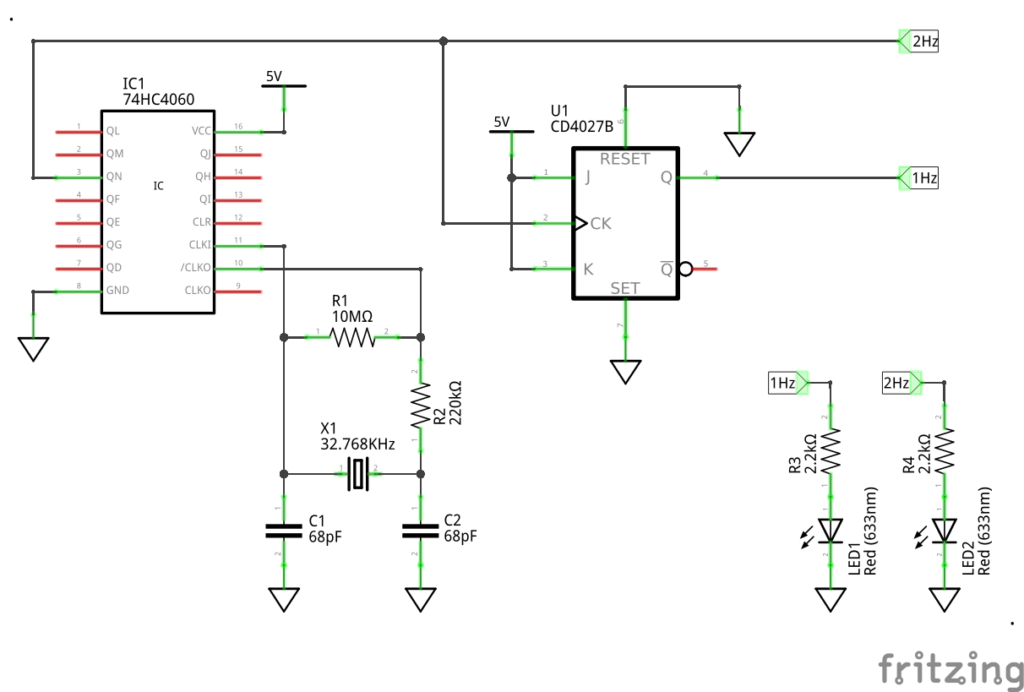

基準クロック回路

基準クロックは、32.768KHz の水晶振動子により、74HC4060 の発振回路を利用して発振します。微調整用のトリマコンデンサを付けていないので、発振周波数の微調整ができません。月差が大きいときは、調整できるようにしたほうがよいでしょう。

32.768KHz は、74HC4060 で 214=16384 分周し、2Hz のパルスを出力します。さらに JK フリップフロップで 2 分周し、基準クロック 1Hz を得ています。

2Hz のパルスは、時刻合わせのためのクロックとして利用します。

デジタル時計 完成!

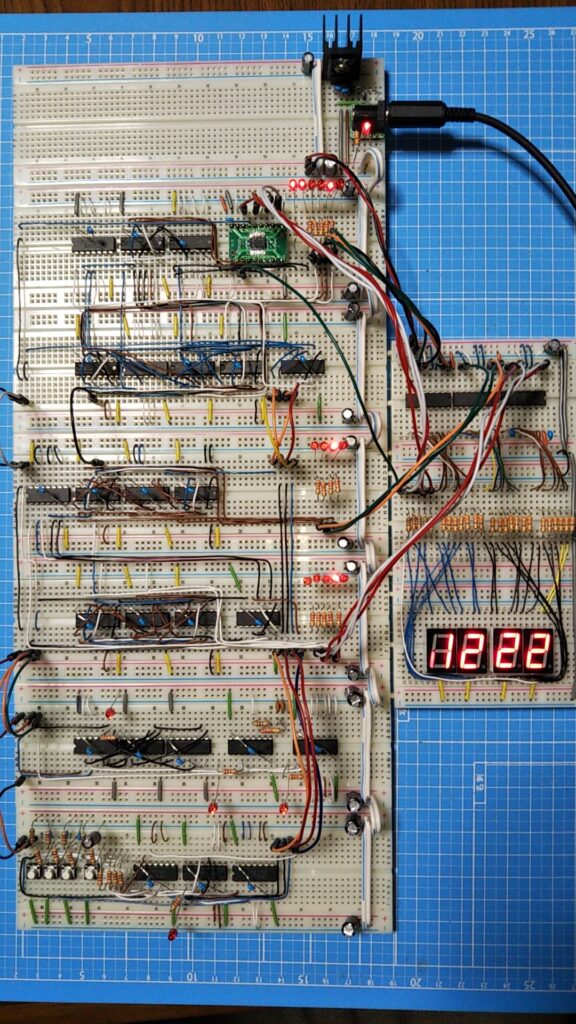

ということで、デジタル時計が完成しました!

ロジック IC 28 個使用。たかだか時刻を表示させるだけなのに、でかい (^_^;)

まぁ、バイナリカウンタ IC とか使うと、けっこう減らせるんだろうと思います。今回は、カウンタ回路の基本の勉強でもあったので使いませんでしたが、次になにかカウンタ回路をつくるときには、利用を考えてみましょう。

図 2 がブレッドボードです。

左側は、下から順番に、時刻合わせ部、基準クロック発振部と秒カウンタ部、分カウンタ (1 位)、分カウンタ (10 位)、時カウンタ部、時カウンタ部 (AM/PM 表示およびラインバッファ)、一番上が 5V 電源部。右側のブレッドボードは、7 セグメント LED 表示器とドライバ部です。

ちなみに、DC5V の電流は約 100mA、消費電力 0.5W となりました。

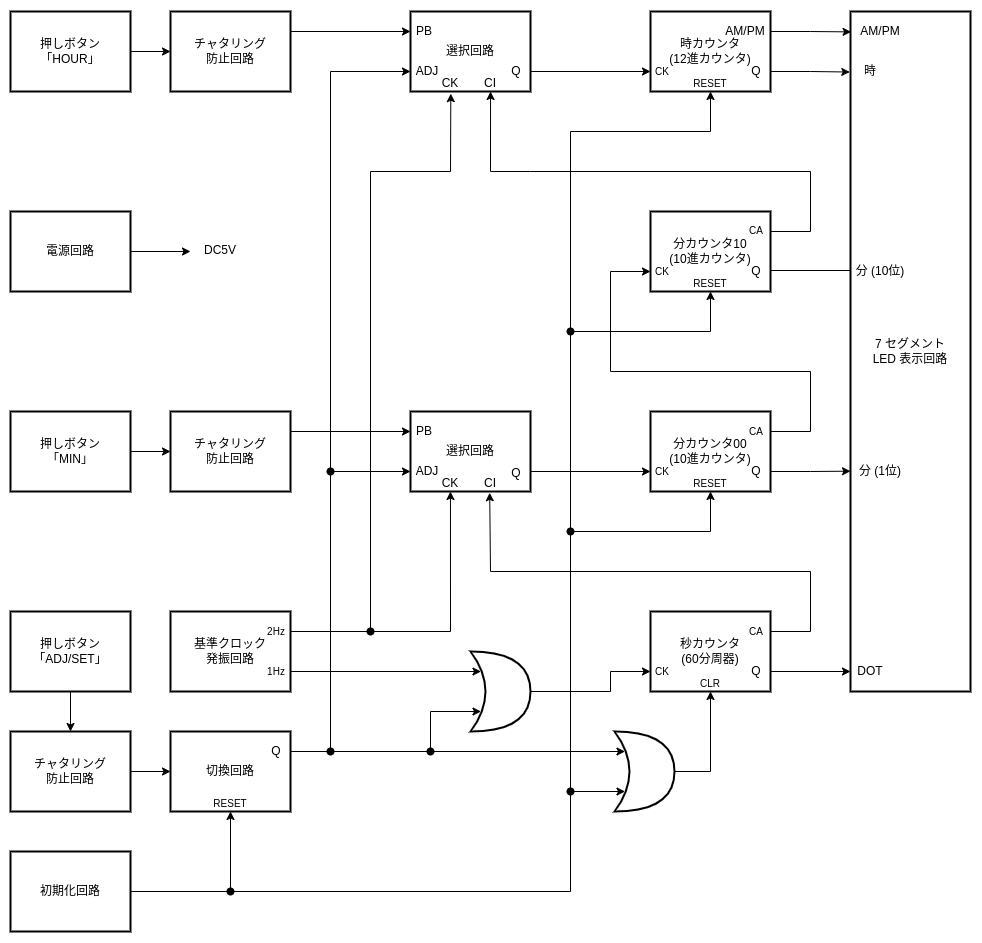

ブロック図

全体のブロック図 (図 3) です。

それぞれの回路は、過去記事を参照下さい。

時刻合わせ切換回路から秒カウンタに至る、途中の OR ゲート。

ひとつは、初期化のため。電源投入時の初期化はすべてのカウンタを対象としますが、時刻合わせ時は秒カウンタのみを初期化します。

もうひとつは、時刻合わせ時に秒カウンタのドット表示を止めるため。

ドット表示だけ止めればいいんだけど、なぜか秒カウンタのクロック入力を止めてる。ま、ちょっとした違和感は、あちこち、いろいろ、あります。m(__)m

製作後記

本来の目的であった、クロック回路の勉強、ってことでのデジタル時計の製作としては、うまくできたんじゃないかと、自賛しております (^_^;)

で、です。カウンタ回路を同期させたい、とか、時刻合わせ回路を改善したい、とか、7 セグメント LED をダイナミック点灯させてみたい、とか、いろいろあるんですが、力尽きた。一部のパーツも底をついた。

ので、「デジタル時計をつくる」シリーズは、これで終了します。

といいつつ、二転三転。

カウンタを同期させるってのは、ブレッドボードを壊す前にちょっとやっておきたい。部分的、基本的なことだけでも試してみたい。と考えております。