前回は、秒カウンタ、分カウンタに使う、同期 60 進カウンタをつくりました。

今回は、時をカウントする同期 12 進カウンタをつくります。

といっても、これまでにつくった 12 進カウンタ (過去記事) に、前回の 10 進カウンタや 6 進カウンタに行なったような改修をしてやれば、よいだけです。つまり、CE 入力でクロックの有効/無効を切り換える、ということ。

おしまい。…… じゃない、です。

フリップフロップを使ったカウンタについては、こちらもあわせてご覧ください。

D フリップフロップを使った同期 12 進カウンタ

ところが、です。

60 進カウンタを 2 組つくったので、JK フリップフロップの在庫が足りなくなりました。なので、前作では、秒カウンタにジョンソンカウンタを使ってみたりした、わけで。今回は、秒カウンタと分カウンタを同じ JK フリップフロップを使った回路にしましたので、そのしわ寄せが時カウンタにおよんできた、というわけで。

部品箱には、D フリップフロップがあります。ので、時カウンタは D フリップフロップを使うことにしました。D フリップフロップでカウンタ回路をつくると、ゲート回路が煩雑になるので嫌いなんですけど、まぁこれも、勉強です。

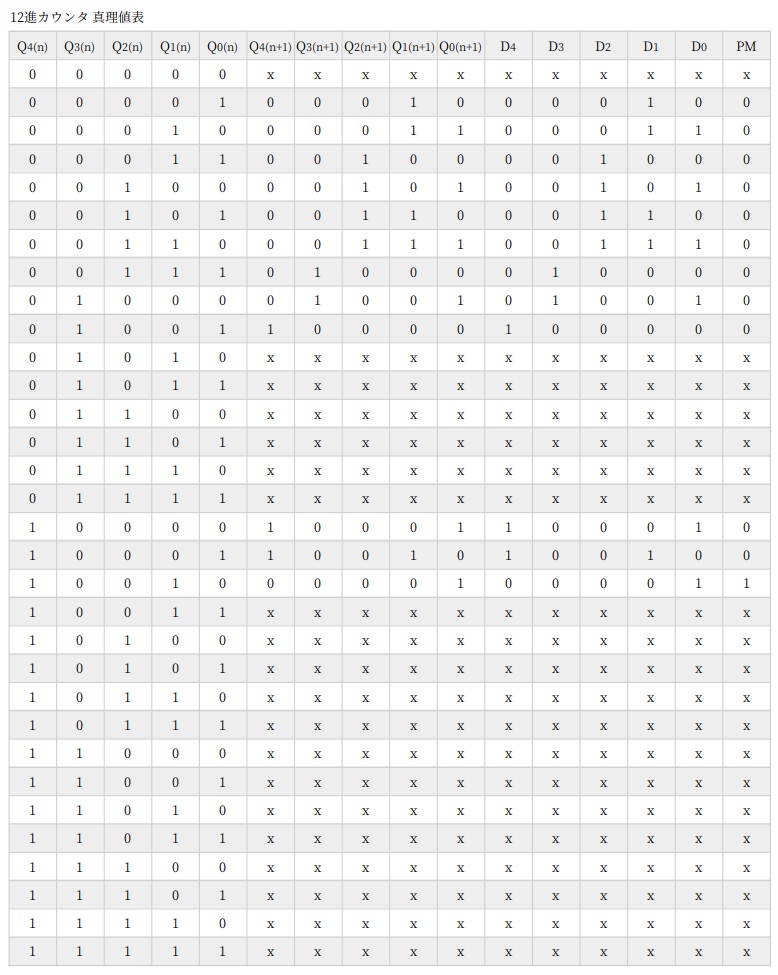

真理値表

時カウンタは、初期値が午前 12 時で、1 時、2 時、…、11 時、午後 12 時、1 時、2 時、…、とカウントしていきます。

出力は、1 位が BCD 4 ビット、10 位は BCD 1ビット。12 時に PM 信号を出力して、午前/午後を切り換えます。

D フリップフロップの場合、D の状態が次の出力になりますから、Q(n+1) の値がそのまま D の値になります。

ってことで、真理値表は図 1 のとおりとなりました。こいつからカルノー図をつくって論理式を求めますが、カルノー図は省略。

ちなみに、JK フリップフロップの場合のカルノー図が過去記事にありますので、参考にして下さい。

論理式

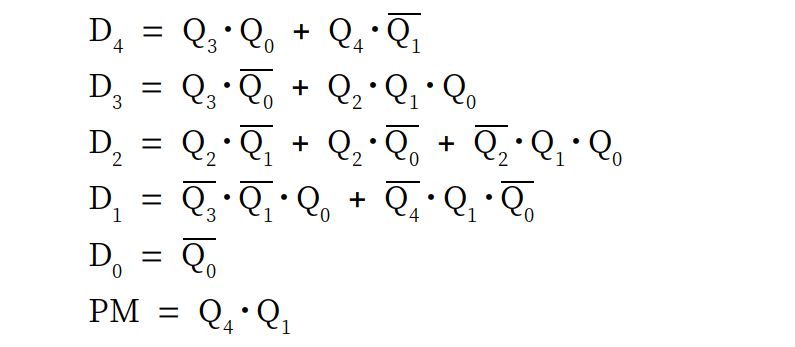

真理値表から求めた論理式は、以下のとおり。

うーん、AND が 14 個と OR が 5 個ぐらいになるんかねぇ。部品箱に多めにあるのは NAND と AND なので、OR は NAND に置き替えたいなぁ。

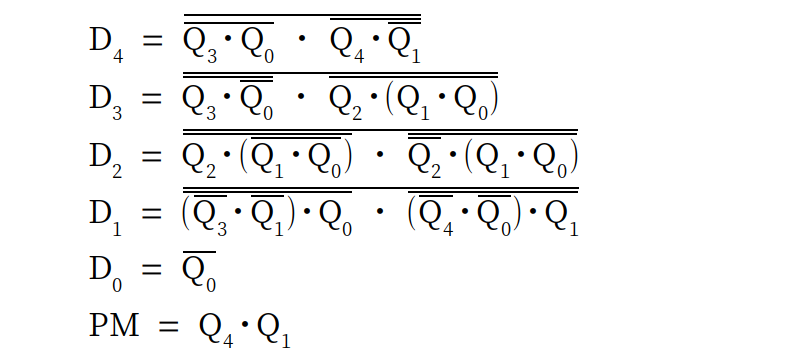

ってことで、論理式をあーして、こーして、

こーなりました。NAND と AND ゲートだけで構成しています。

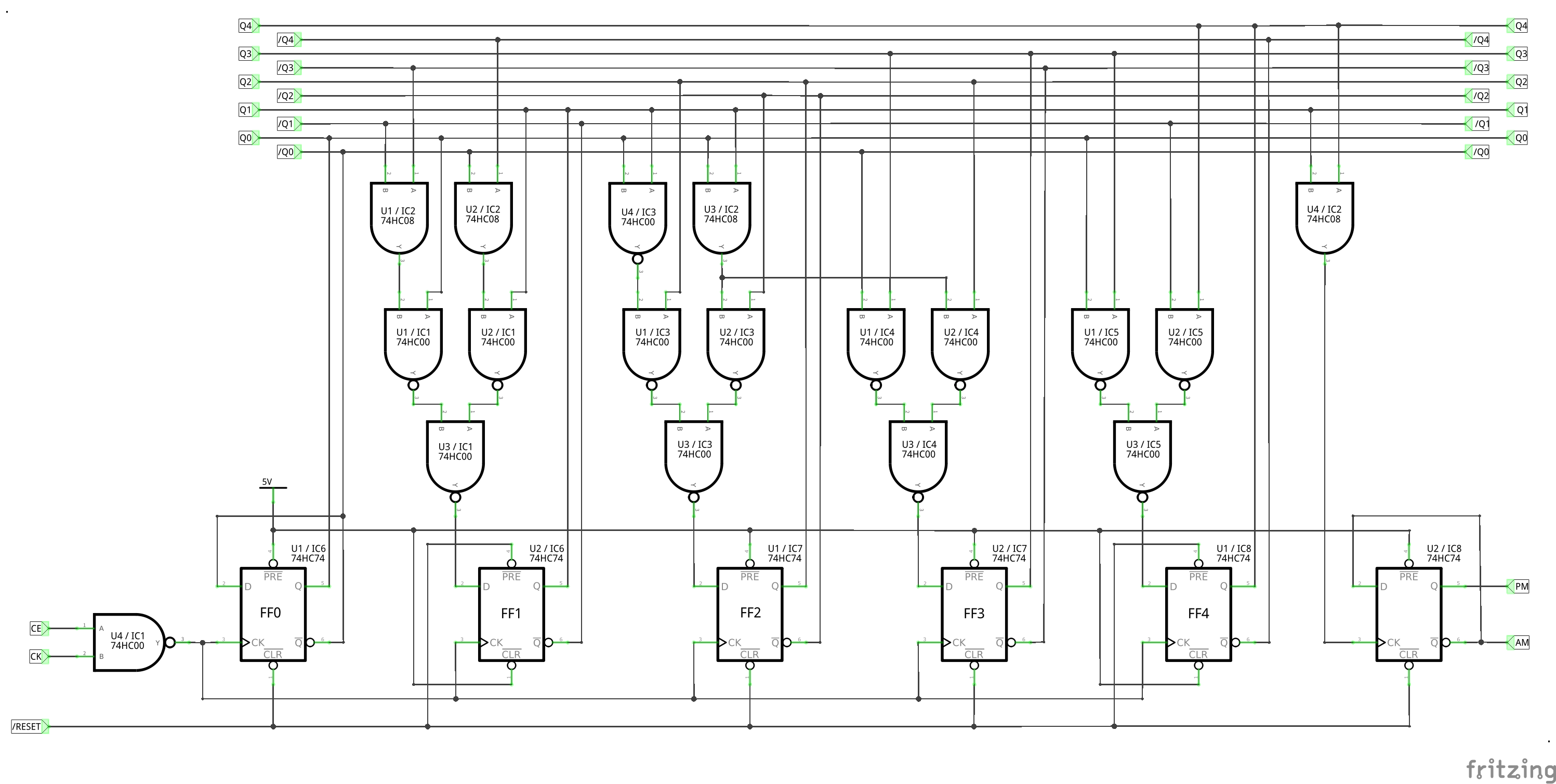

回路図

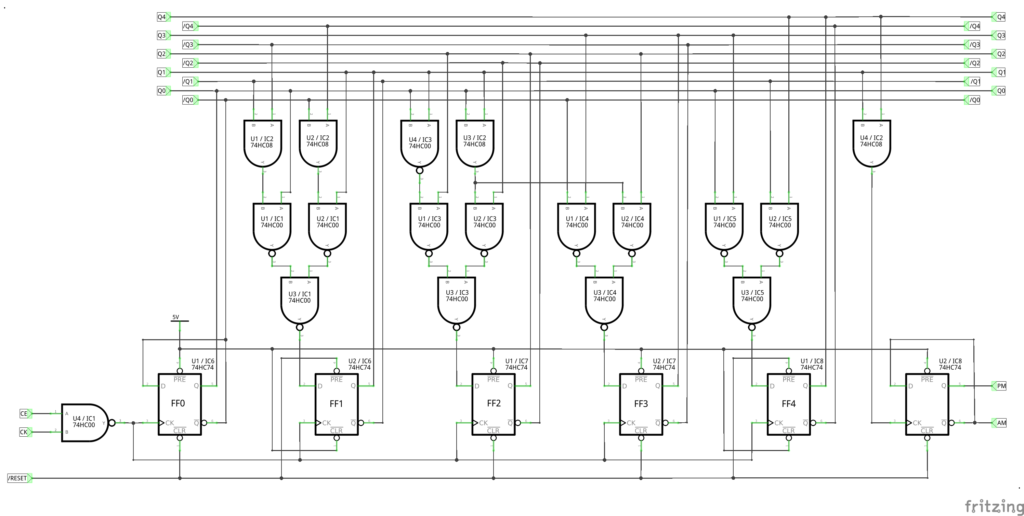

論理式から、図 2 のように、カウンタ回路をつくりました。

クロックは CE が HIGH のときに有効になります。10 進カウンタ、6 進カウンタと同様です。

初期化時、12 時 にプリセットするため、FF1 と FF4 の PRE と CLR の接続が逆になっています。また、初期化はアクティブローなので、リセット信号も RESET にしています。

PM 出力は、T フリップフロップで午前/午後にトグルします。

ゲート回路 (組み合わせ回路) が煩雑でしょ? これだから D フリップフロップは … (^_^;)

次回は

カウンタ回路が、すべてできましたので、次回は時刻合わせ回路をつくりましょう。

時刻合わせの方法は、前作とおなじです。が、カウンタを同期させたおかげで、不具合が解消できるんじゃないかと。当初考えていたような時刻合わせが、たぶん、うまくできる、よーな気がします。