これまでに、秒、分、時をカウントする回路ができあがりました。

時計のような形になっていますが、時刻合わせができなければ時計の用をなさないのです。

なので、今回は、時刻合わせ回路をつくり、デジタル時計を完成させましょう。

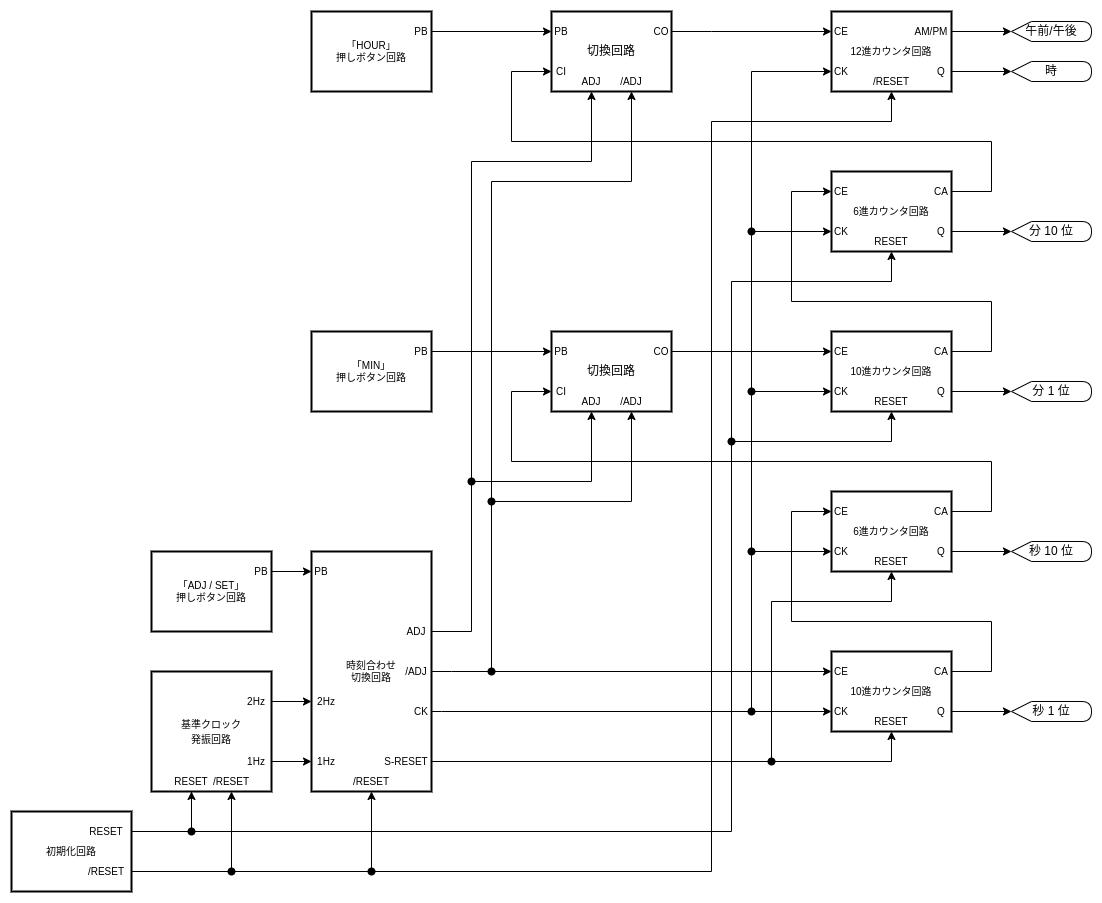

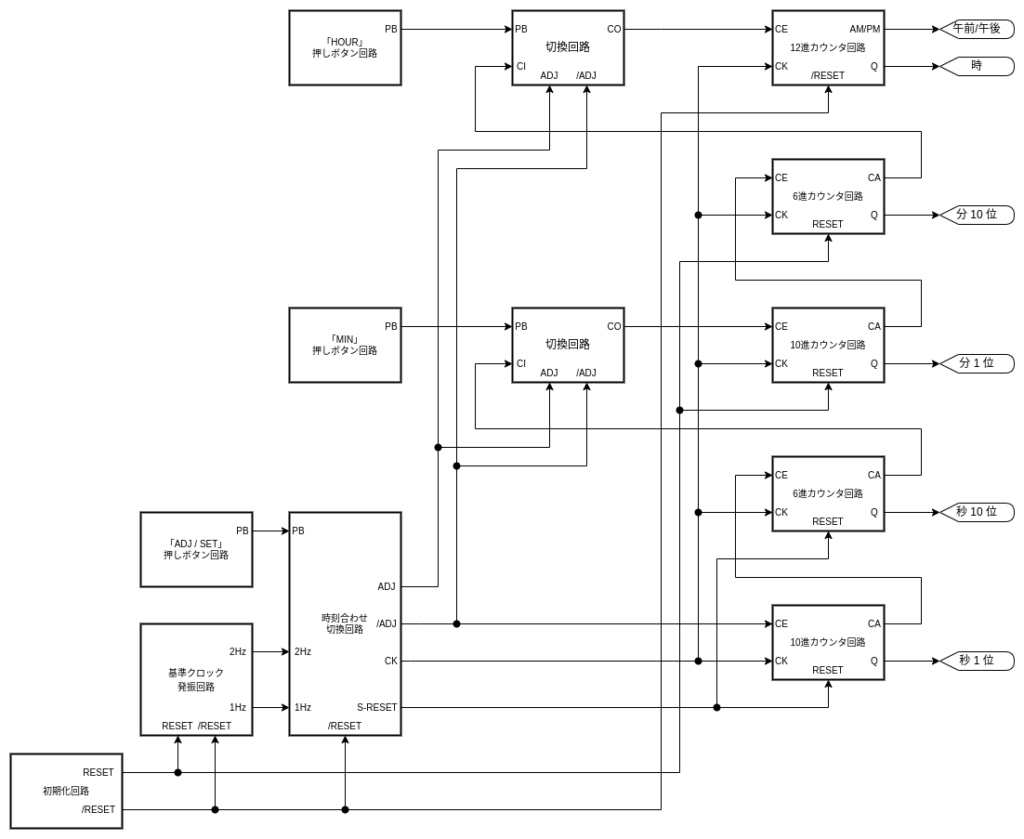

ブロック図

デジタル時計のブロック図 (再掲) を確認しましょう。

時刻合わせは、時刻合わせ切換回路と、分、時カウンタの切換回路、押しボタン回路などで行ないます。

時刻合わせ操作は、「ADJ/SET」ボタン押下で時刻合わせモードにはいり、「HOUR」「MIN」ボタンで時分を合わせ、「ADJ/SET」ボタン押下で 0 秒スタートさせる、ように行ないます。時分を合わせるには、2Hz のクロックを時カウンタ、分カウンタに与え、ボタン押下中に表示を早送りさせます。秒カウンタは 0 秒にリセットし、停止。「ADJ/SET」ボタン押下で通常モードにもどると、カウントを開始します。

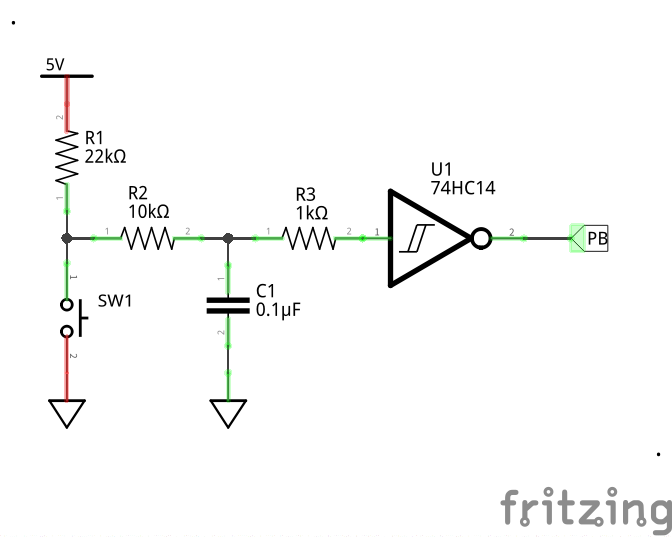

押しボタン回路

押しボタン回路は、時刻合わせモード切換え「ADJ/SET」、時合わせ「HOUR」、分合わせ「MIN」の 3 組つくります。

ごく普通のチャタリング除去の回路。CR の時定数は、まぁテキトーです。

R3 は、シュミットインバータの保護抵抗です。つけておかないと、インバータが壊れます。壊れるかもしれません。壊れても知りません。

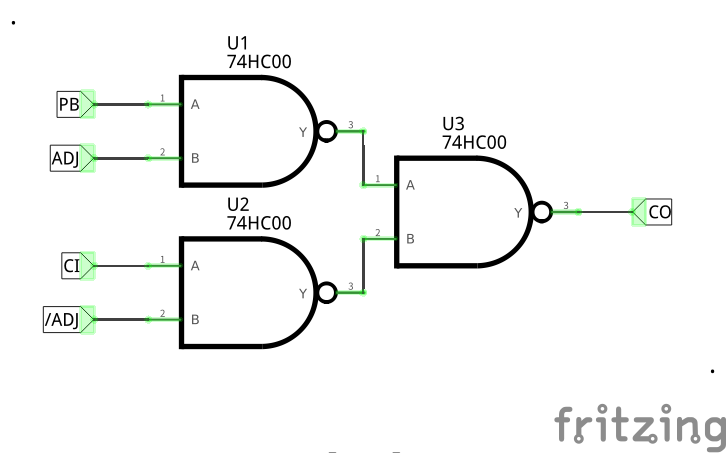

カウンタ切換回路

カウンタ切換回路。んー、名称がいまいちだな (;´Д`)

分カウンタ、時カウンタの CE に渡す信号を切換えます。

通常モード時は、ADJ = LOW、ADJ = HIGH です。このときは、CI が CO へ出力されますので、下位カウンタの CA が、上位カウンタの CE へ渡される。

時刻合わせモード時は、ADJ = HIGH、ADJ = LOW なので、押しボタン信号 PB が CO へ出力されます。押しボタンを押しているとき、CE へ HIGH が渡されるので、カウンタが動きます。このとき、カウンタへ 2Hz のクロックをいれることで、カウンタが早送りされます。押しボタンを離すと、カウンタは停止します。

この回路、いわゆる「マルチプレクサ」っていう論理回路です。

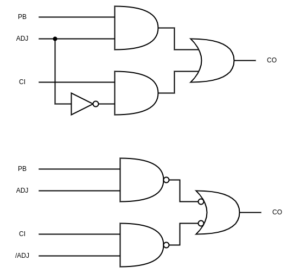

マルチプレクサは、教科書には、図 4 上のような回路がでてきますね。NOT と AND と OR を使った回路。

こいつを下のようにちょっと書き換えてやると、NAND だけになる。論理式など考えるまでもなく、回路みればすぐわかりますね。負理論入力 OR は、イコール NAND ですよ。

これで 4 回路入り IC 1 個でできる。

選択信号は、後述する時刻合わせ切換え回路のフリップフロップの出力を使うので、NOT も不要です。

反転した信号がなければ、1 個余っている NAND を使うって手もありますね。要するに、2 入力マルチプレクサは NAND IC 1 個でできる、ってこと。

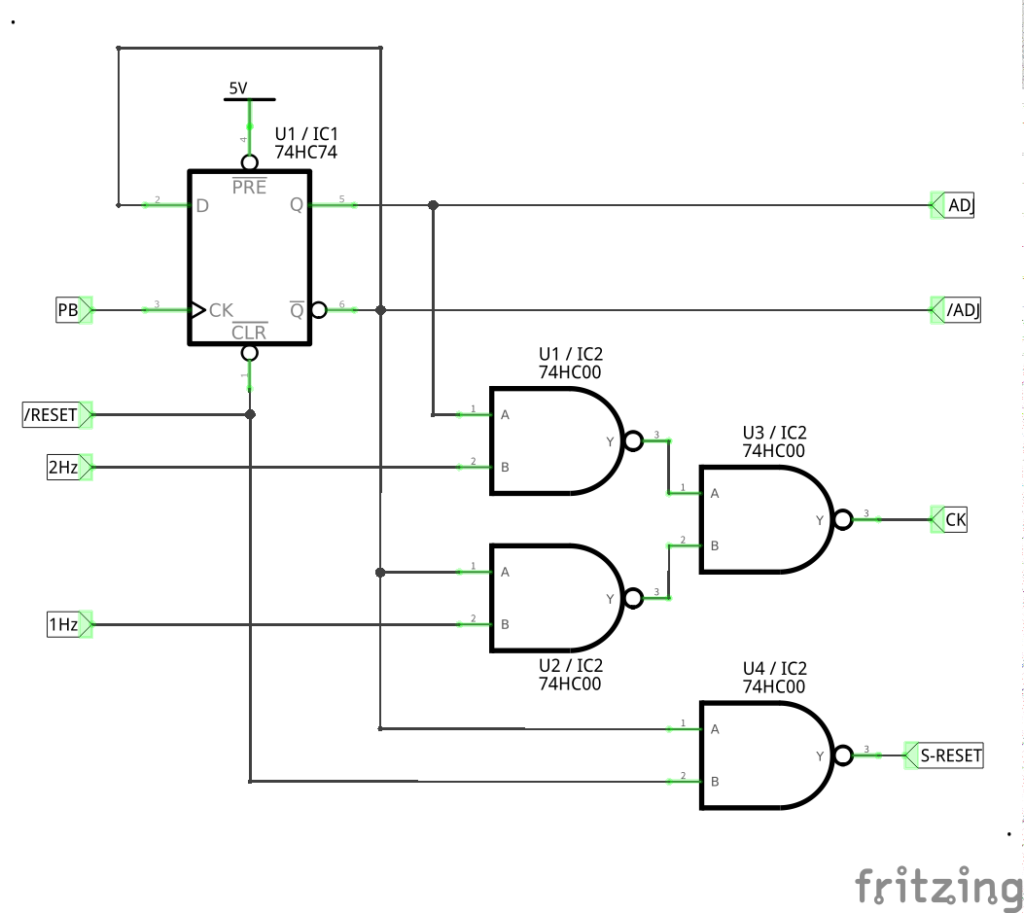

時刻合わせ切換回路

D フリップフロップは、T フリップフロップの動作をしています。

時刻合わせモード切換え押しボタンの出力 PB をクロックとして入力すると、出力 ADJ がトグルします。これにより、通常モードと時刻合わせモードを切り換えています。

NAND の U1~U3 は、マルチプレクサです。クロックの周期を切り換えます。通常モードでは 1Hz、時刻合わせモードでは 2Hz のクロックを CK へ出力します。

U4 は、時刻合わせモード時、秒カウンタをリセットし、停止する信号 S-RESET です。

時刻合わせ動作の概要

時刻合わせモードの動作を、確認しておきます。

「通常モード」

各カウンタへ送られるクロックは 1Hz です。

秒カウンタ、分カウンタから出力される CA (桁上がり) は、上位カウンタの CE (カウンタ有効) へ送られます。

これにより、各カウンタは、秒、分、時をそれぞれカウントします。

「時刻合わせモード」

押しボタン「ADJ/SET」を押下すると、時刻合わせモード (ADJ=HIGH) に切り換わります。各カウンタへ送られるクロックは 2Hz になります。秒カウンタへリセット信号 S-RESET が送られると、カウンタが 0 秒にセットされ、停止、待機します。

分カウンタ、時カウンタの CE は、それぞれ分合わせ押しボタン「MIN」、時合わせ押しボタン「HOUR」の出力を受け取ります。押しボタンを押すと CE が有効になり、カウンタは 2Hz のクロックによりカウントアップします。押しボタンを離すと CE は無効になり、カウンタは停止、待機します。

「0 秒セット」

再度「ADJ/SET」ボタンを押すと、通常モードに戻ります。クロックは 1Hz になります。

秒カウンタは 0 秒からスタートします。ただし、クロックが 1Hz なので、1 秒未満の誤差が生じます。これは仕様です (^_^;)

CA は上位の CE へ送られますので、時刻合わせした時、分から、カウントを再開します。

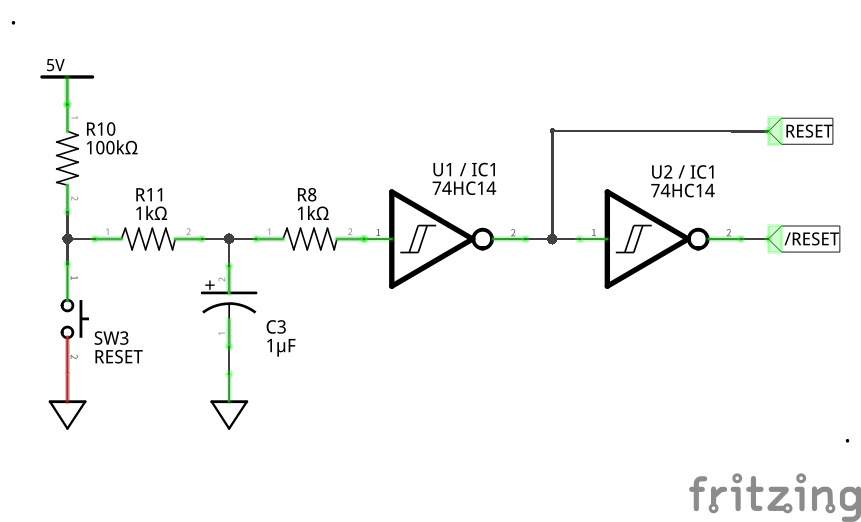

初期化回路

電源投入時に、初期化パルスを出力し、各フリップフロップを初期化します。JK フリップフロップ用のアクティブハイ RESET と、D フリップフロップ用のアクティブロー RESET が出力されます。

押しボタンを押したときも、出力されます。

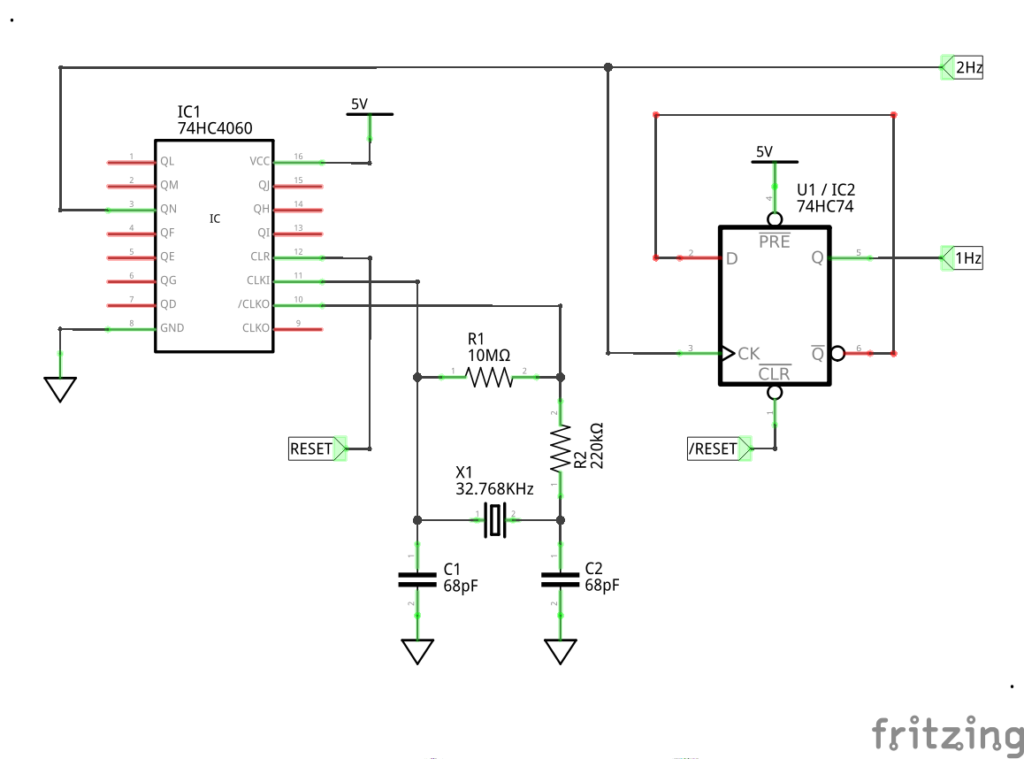

基準クロック発振回路

32.768KHz 水晶振動子による基準クロック発振回路です。

74HC4060 を使って 214 = 16384 分周し、2Hz を取りだしています。D フリップフロップで、さらに 2 分周し、1Hz にします。

2Hz パルス信号は時刻合わせに、1Hz パルス信号は時刻カウントの基準クロックに、それぞれ使用します。

なお、デジタル時計の平均月差は ±30 秒だそうです。誤差が大きいときは、トリマコンデンサを入れるなどして、発振周波数を調整してください。

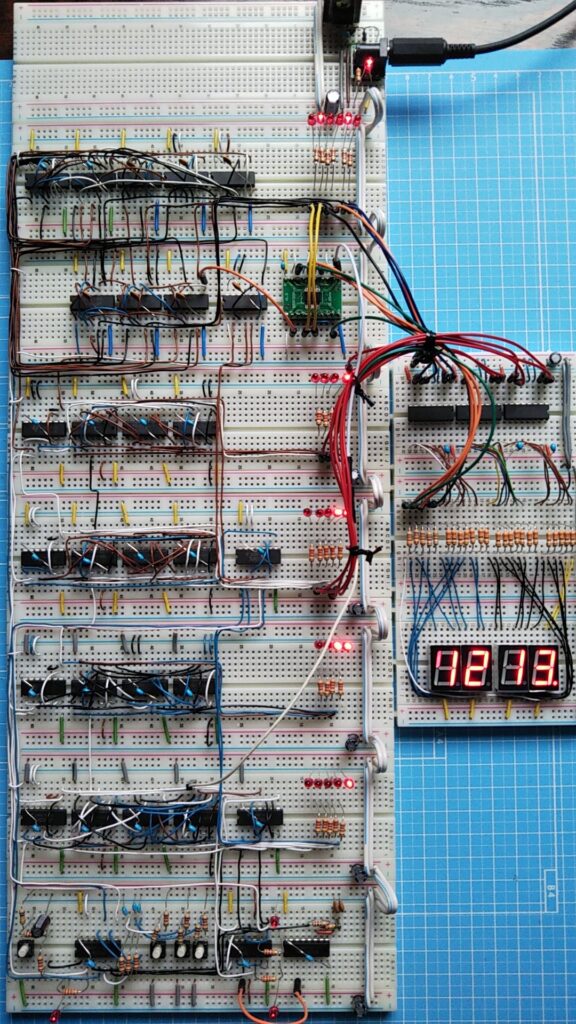

製作後記

前作をつくってから、やっぱり時刻合わせがうまくないのが気になってました。あわせて、カウンタを同期させる方法も考えてました。で、同期させることで、時刻合わせの不具合も解消できるんじゃね?って気がついて、改修することに。

まぁ、「低機能」ってところに変わりはないですが、デジタル時計として、ふつーに使える程度の回路にはなったんじゃないかな。とりあえず、自分的には、満足してます。

今回は、時刻表示回路については、特に考えていません。前作でつくった 7 セグメント LED 表示回路をそのまま利用しています。時分秒ともに BCD で出力されてますので、お好みでつくってもらえばいいんじゃないかと。

ただまぁ、7 セグメント LED のダイナミック点灯ってのはやってみたいので、次はそのあたりを考えてみようかなと、計画はしてます。

と、ゆーことで、ロジック IC でつくるデジタル時計の巻、終了します。